**FAIRCHILD**

A Schlumberger Company

## The Solid State Imaging Technology

**FAIRCHILD Camera & Instrument (UK) Ltd.**

230 High Street, Potters Bar, Hertfordshire EN6 5BU England

Tel: Potters Bar (0707) 51111, Telex: 262835

and information is placed within rings further security levels, specify precisely the requirements.

## ecast

W firmly established

dium and large scale

nd orders for such

sent some two fifths

nue increased 26%

months of this year.

said Mr Macdonald,

try into the small

ctor; we have intro-

new series of small

ms and we have an

se of a very powerful

ns in our business

,

B700 and B1700

sors and the L8000

mini computers he

s of these new pro-

er growth rates for

resents one third of

s from historical

year up to a growth

the first nine months

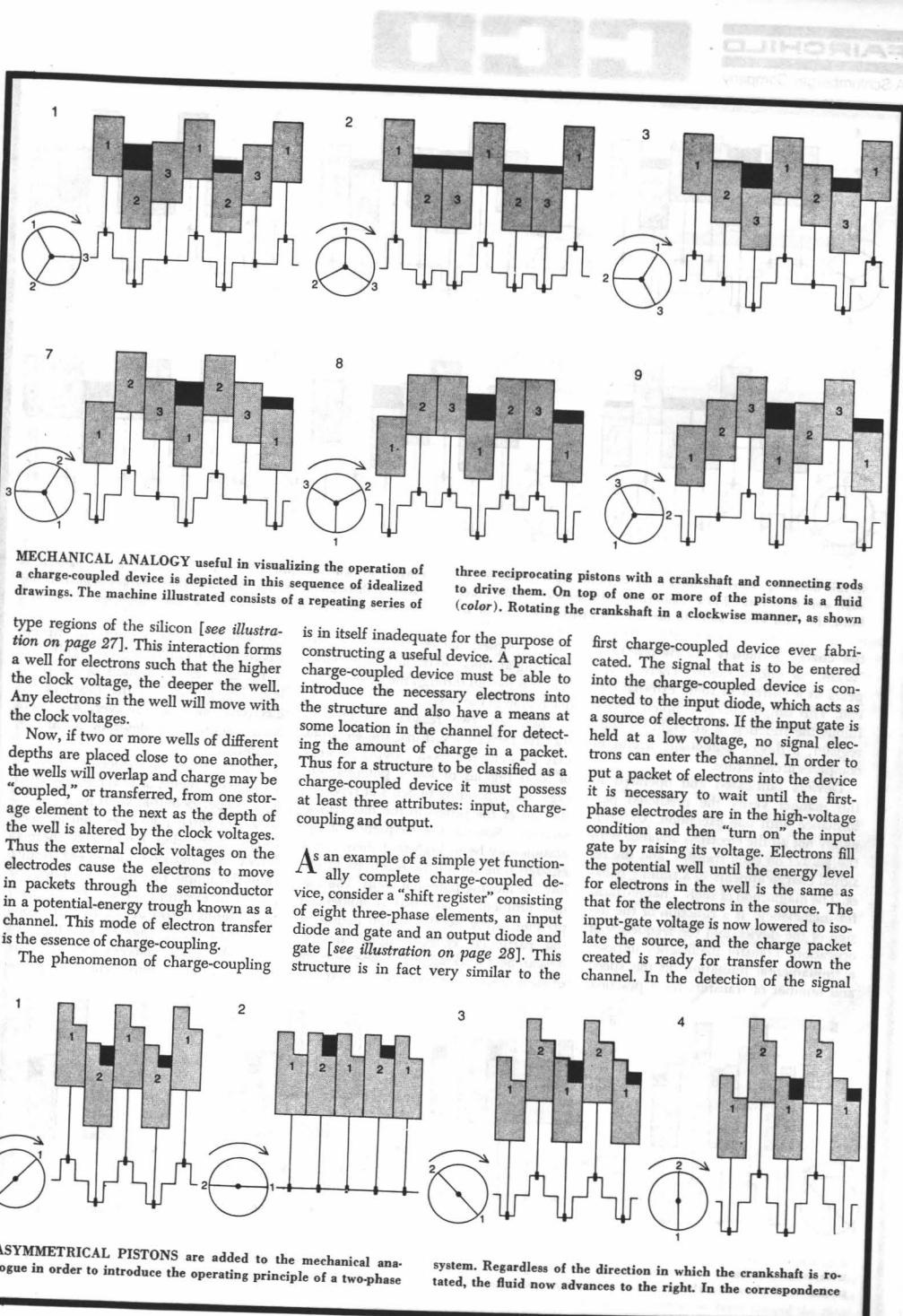

## Charge coupled area image sensor

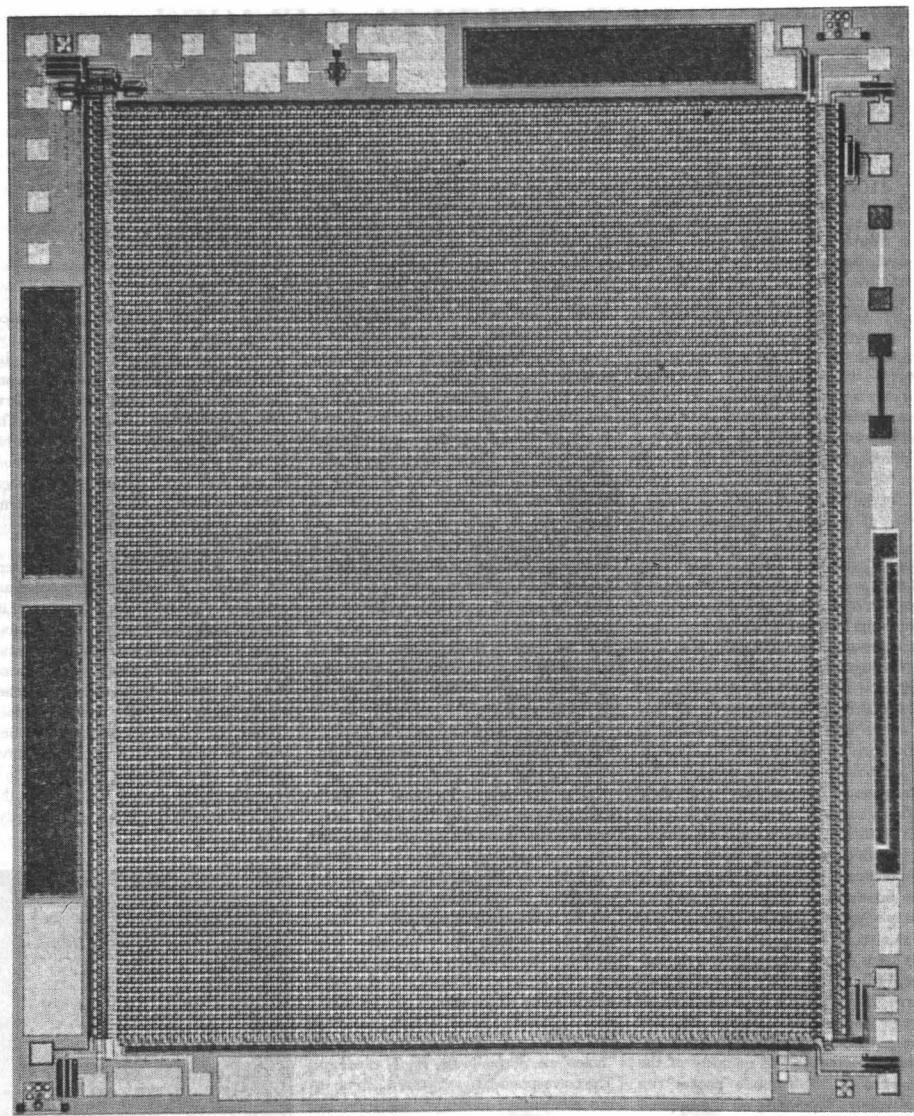

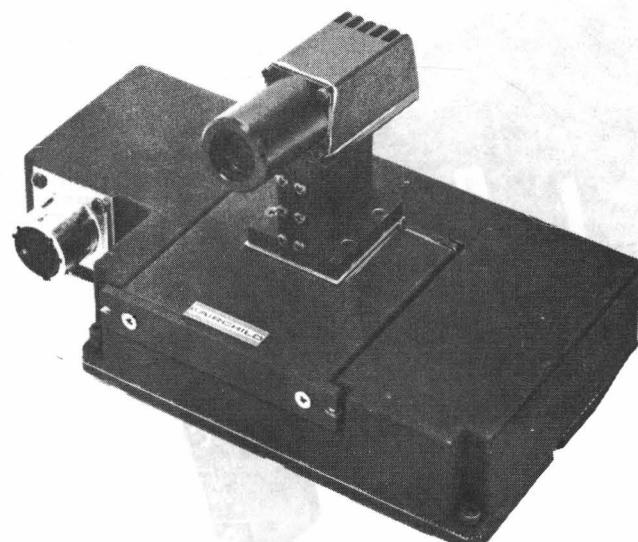

Fairchild Camera and Instrument Corporation has announced what is said to be 'the world's first commercially available charge coupled area image sensor'.

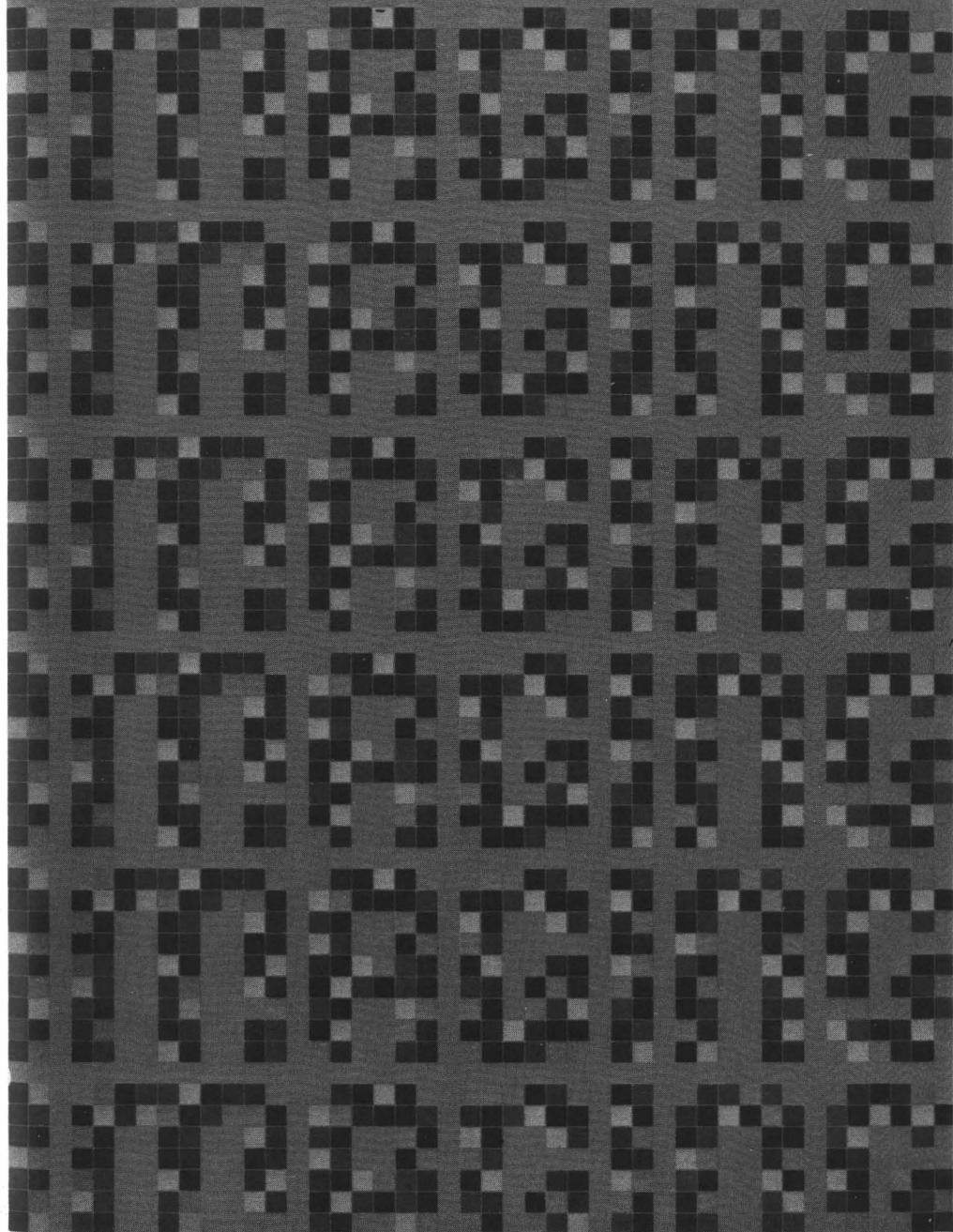

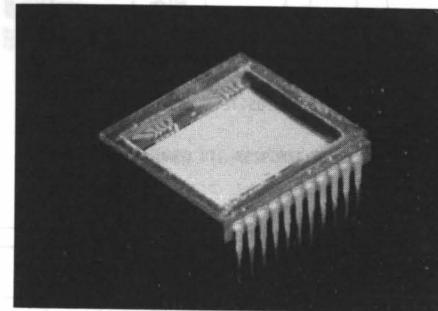

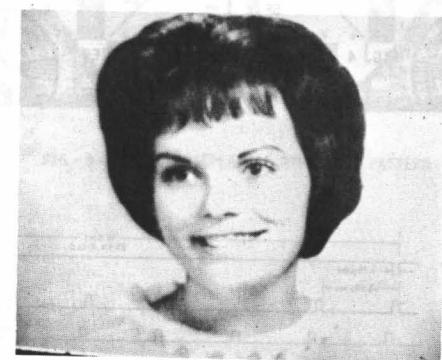

The device, the CCD-201, uses an array of  $100 \times 100$  solid state elements to create a television picture signal directly from light focused on the surface of the sensor.

The sensor is based on a new semiconductor technology called charge coupling which utilises electrical charges to collect, store and transfer information through small chips of silicon. Compared to other image sensors, CCD's are extremely sensitive to light and less subject to electrical noise and other effects that degrade signals.

The CCD-201 operates from 20V compared with the 2kV of typical vacuum tube image sensors. Nominal power consumption is 50mW.

The array of light sensitive elements is arranged in 100 columns of 100 elements, with each element measuring  $1.2 \times 0.8\text{ mil}$ . These columns are spaced  $1.6\text{ mil}$  apart horizontally and  $1.2\text{ mil}$  apart vertically to create the standard  $3 \times 4$  aspect ratio. Inherent spatial accuracy of the device is 1 part in 10 000.

The device is in a 24 lead DIP measuring  $0.5 \times 1.25\text{ in.}$

22 NOV 1973

## CCD IMAGING AND SIGNAL PROCESSING

|                                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

| Introduction .....                                                                  | 2    |

| Datasheets .....                                                                    | 6    |

| CCD 111 .....                                                                       | 7    |

| CCD 121 .....                                                                       | 23   |

| CCD 122/142 .....                                                                   | 30   |

| CCD 133/143 .....                                                                   | 46   |

| CCD 211/221 .....                                                                   | 61   |

| CCD Camera Subsystems .....                                                         | 73   |

| CCD Line Scan Cameras 1100, 1300, 1400 .....                                        | 75   |

| Industrial Line Scan Cameras 1100 .....                                             | 88   |

| Area Camera Subsystems .....                                                        | 94   |

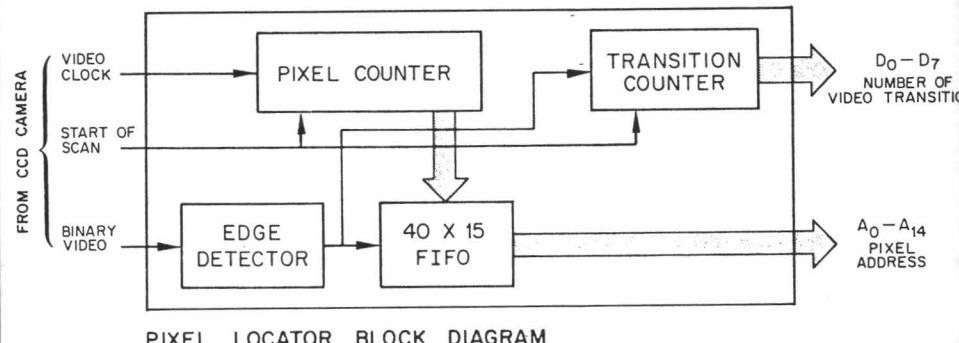

| Pixel Locator .....                                                                 | 98   |

| CCD Design Aids .....                                                               | 100  |

| LID II .....                                                                        | 101  |

| CCD 133 DB / 143 DB .....                                                           | 103  |

| CCD Signal Processing .....                                                         | 106  |

| CCD 321 A .....                                                                     | 108  |

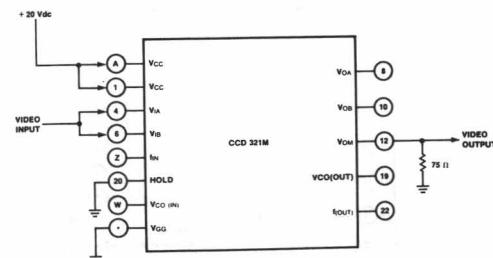

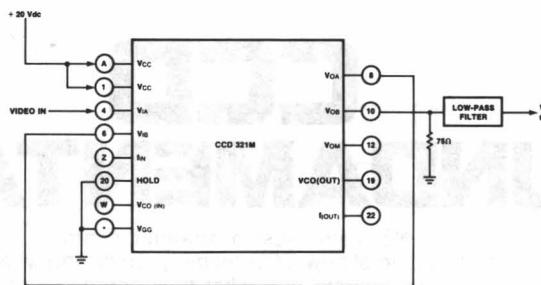

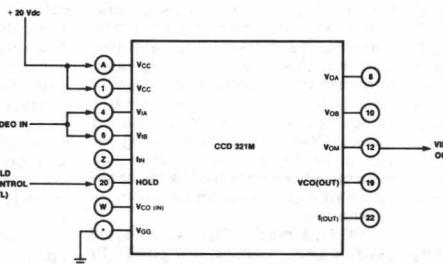

| CCD 321 M .....                                                                     | 116  |

| Application / Physic .....                                                          | 122  |

| CCD Fundamentals .....                                                              | 122  |

| Charge Coupled Devices .....                                                        | 127  |

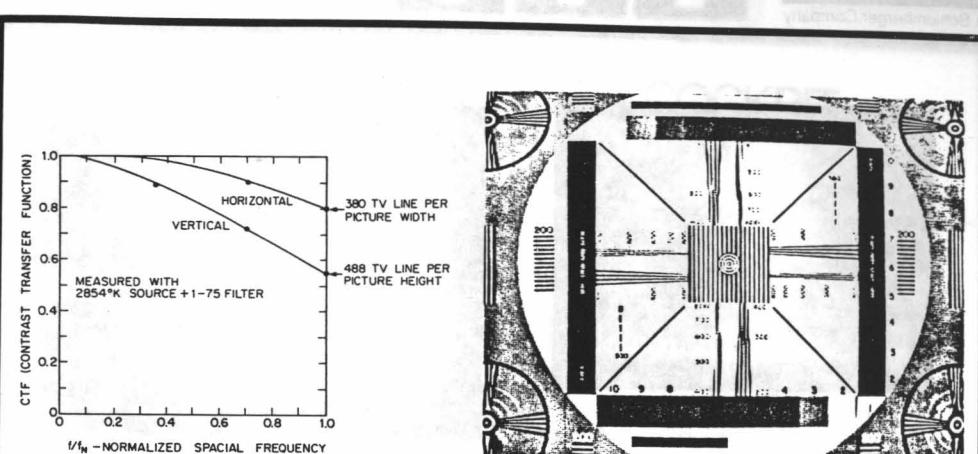

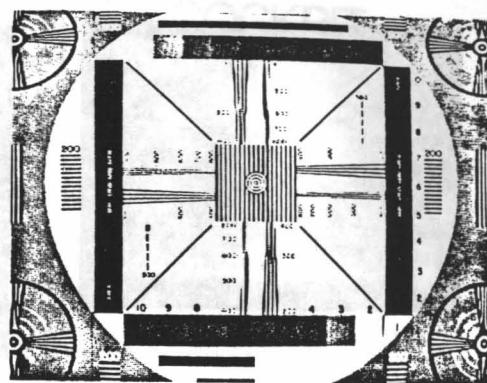

| Performance Characteristics of producible NTSC compatible<br>CCD Image Sensor ..... | 137  |

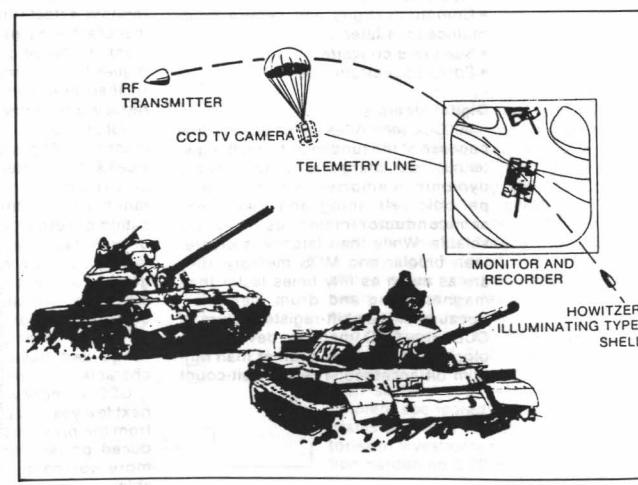

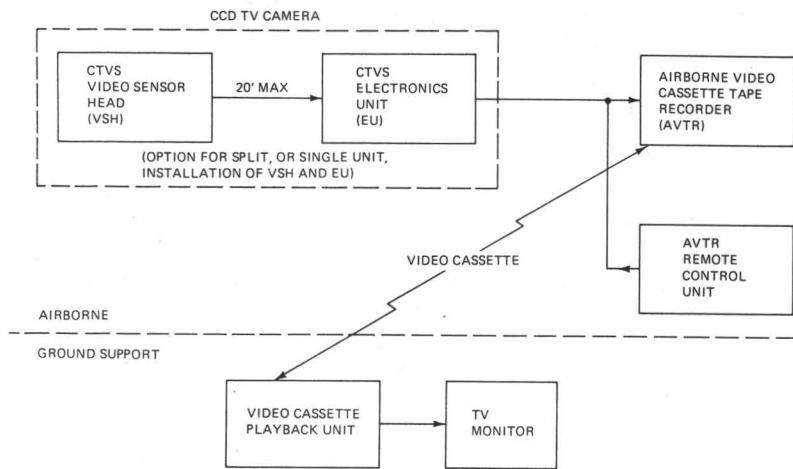

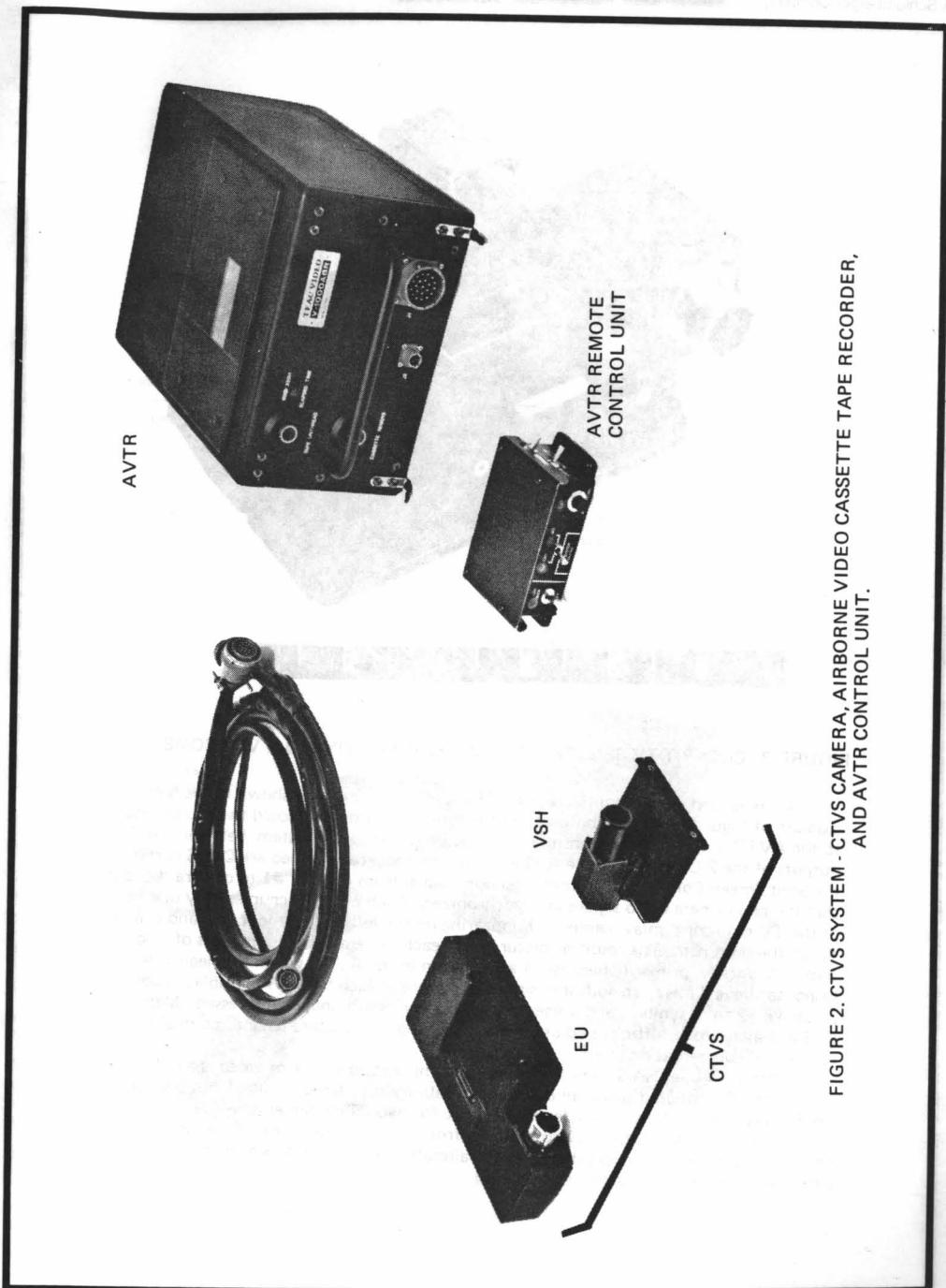

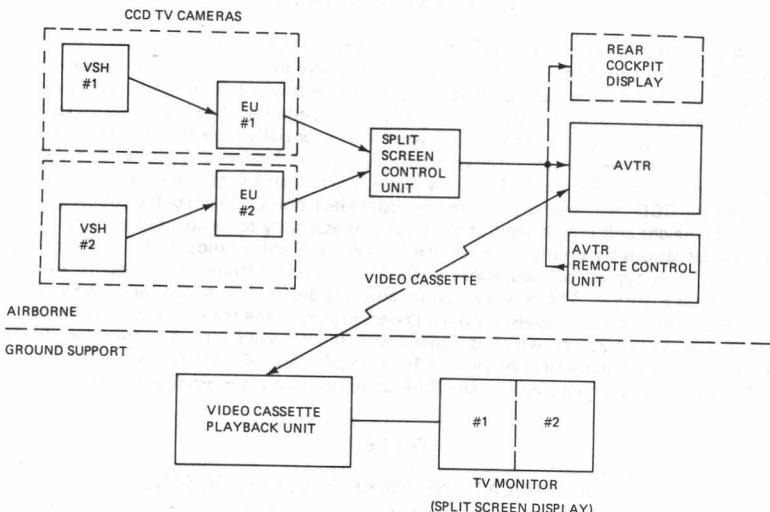

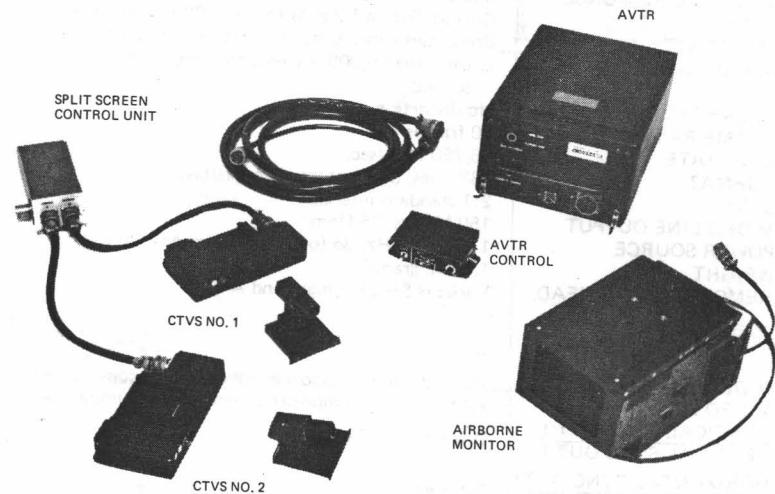

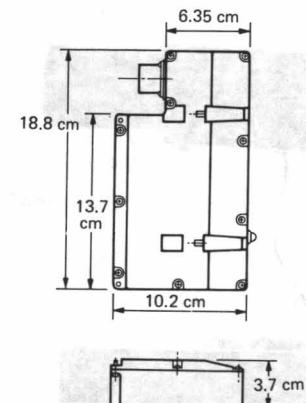

| Solid State Cockpit TV System .....                                                 | 145  |

# Introduction

## Line Scan Image Sensors

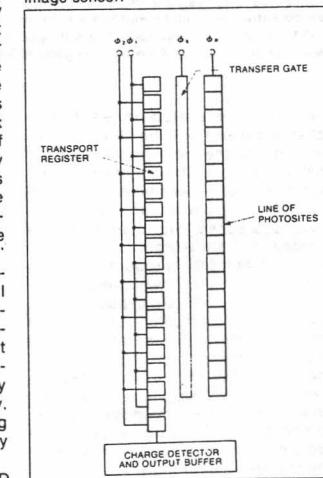

Basically, a line scan image sensor is composed of a row of image sensing elements (photosites), two analog transport registers, and an output amplifier. Light energy falls on the photosites and generates charge packets proportional to the light intensity. These charge packets are then transferred in parallel to two analog transport registers, which are clocked by 2-phase clocks. The packets are next delivered to an on-chip output amplifier where they are converted to proportional voltage levels. A series of pulses, amplitude modulated with the optical information, appear at the output.

The following tables summarize the features of Fairchild's Line Scan Imaging Products. The CCD122, CCD133, CCD142, and CCD143 are second generation image sensors which include additional integrated CCD and MOS circuitry for generation and amplification of clock signals, generation of white and black reference levels for the

video output signal, generation of an end-of-scan output, and a video sample-and-hold circuit.

Key advantages of Fairchild CCD line scan sensors, due to Fairchild's Isoplanar buried-channel structure, include high data rates, high charge transfer efficiencies, low noise, and relatively small die sizes.

Line scan sensors find applications ranging from optical character recognition (OCR) using the 256 x 1 device to high speed facsimile sensing using the 1728 x 1 or 2048 x 1. The precise location of the photosites on the sensor allows the device to be used in high precision non-contact measurement applications such as dimensional measurements of objects, shape recognition and sorting, and defect detection. The line scan sensors have the same sensing element center-to-center spacing; selection is determined by the user's resolution requirement.

\* ADC 53-33

\* BDC 99-45

\* 357.80

533.30

642.60

| Ordering Code | Number of Elements | Element Size - Microns | Maximum Data Rate | Dynamic Range (Typical) | Responsivity (Typical)             |

|---------------|--------------------|------------------------|-------------------|-------------------------|------------------------------------|

| CCD111DC      | 256x1              | 13x17                  | 10MHz             | 2500:1                  | 0.5V per $\mu\text{J}/\text{cm}^2$ |

| CCD133DC      | 1024x1             | 13x13                  | 20MHz             | 2500:1                  | 3.0V per $\mu\text{J}/\text{cm}^2$ |

| CCD121HC      | 1728x1             | 13x17                  | 10MHz             | 2500:1                  | 0.5V per $\mu\text{J}/\text{cm}^2$ |

| CCD122DC      | 1728x1             | 13x13                  | 2MHz              | 2500:1                  | 3.5V per $\mu\text{J}/\text{cm}^2$ |

| CCD142DC      | 2048x1             | 13x13                  | 2MHz              | 2500:1                  | 3.5V per $\mu\text{J}/\text{cm}^2$ |

| CCD143DC      | 2048x1             | 13x13                  | 20MHz             | 2500:1                  | 3.0V per $\mu\text{J}/\text{cm}^2$ |

### Line Scan Sensors

| Ordering Code | Sensor Supported | Comments                                                                                                                                                                                                                                                                                                                                                            |

|---------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCD111DB      | CCD111DC         |                                                                                                                                                                                                                                                                                                                                                                     |

| CCD133DB      | CCD133DC         |                                                                                                                                                                                                                                                                                                                                                                     |

| CCD121HB      | CCD121HC         |                                                                                                                                                                                                                                                                                                                                                                     |

| CCD122DB      | CCD122DC         |                                                                                                                                                                                                                                                                                                                                                                     |

| CCD142DB      | CCD142DC         |                                                                                                                                                                                                                                                                                                                                                                     |

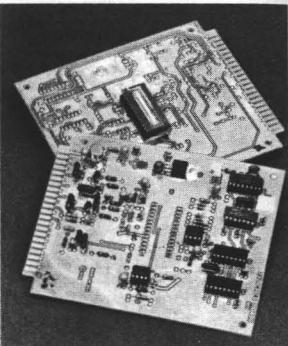

| CCD143DB      | CCD143DC         | Fairchild offers a series of printed circuit boards for use as construction aids for experimental systems using CCD line scan image sensors. These design and development boards are fully assembled and tested, and require only power supplies and an oscilloscope to display the video information corresponding to the image positioned in front of the sensor. |

### Line Scan Design Aids (Do not include Sensors)

| Ordering Code | Number of Elements | Line Scan Rate | Exposure Time           | Data Rate    |

|---------------|--------------------|----------------|-------------------------|--------------|

| CCD1100C      | 256x1              | 60Hz-35kHz     | 30 $\mu\text{s}$ -16ms  | 100kHz-10MHz |

| CCD1200C      | 512x1              | 60Hz-20kHz     | 51 $\mu\text{s}$ -16ms  | 100kHz-10MHz |

| CCD1300C      | 1024x1             | 60Hz-10kHz     | 102 $\mu\text{s}$ -16ms | 100kHz-10MHz |

| CCD1400C      | 1728x1             | 60Hz- 6kHz     | 175 $\mu\text{s}$ -16ms | 100kHz-10MHz |

| CCD1500C      | 2048x1             | 60Hz- 5kHz     | 204 $\mu\text{s}$ -16ms | 100kHz-10MHz |

### Line Scan Camera Subsystems

(Include Camera, Control Unit and Interconnect Cables. Order Lens separately.)

Camera only may be ordered.

| Ordering Code | Number of Elements | Grade | Dynamic Range (Typical) | Responsivity (Typical)           | Maximum Frame Rate |

|---------------|--------------------|-------|-------------------------|----------------------------------|--------------------|

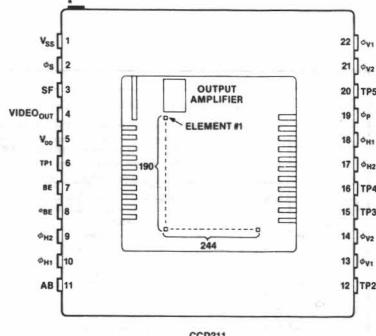

| CD211ADC      | 244x190            | A     | 1000:1                  | 5V per $\mu\text{J}/\text{cm}^2$ | 240/s              |

| CD211BDC      | 244x190            | B     | 1000:1                  | 5V per $\mu\text{J}/\text{cm}^2$ | 240/s              |

| CD211CDC      | 244x190            | C     | 1000:1                  | 5V per $\mu\text{J}/\text{cm}^2$ | 240/s              |

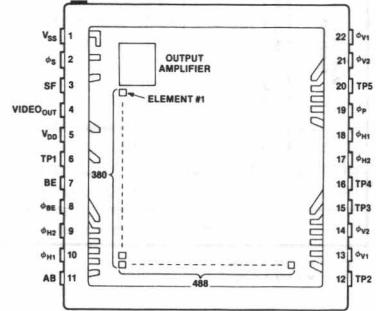

| *CD221ADC     | 488x380            | A     | 1000:1                  | 5V per $\mu\text{J}/\text{cm}^2$ | 60/s               |

| *CD221BDC     | 488x380            | B     | 1000:1                  | 5V per $\mu\text{J}/\text{cm}^2$ | 60/s               |

### Area Sensors

\*NTSC Compatible

| Ordering Code | Number of Elements | Maximum Frame Rate | Comment              |

|---------------|--------------------|--------------------|----------------------|

| CCD2000C      | 488x380            | 60Hz               | Full NTSC Resolution |

| CCD2100C      | 244x190            | 240Hz              | 1/4 NTSC Resolution  |

### Area Camera Subsystems

(Include Camera, Control Unit and Interconnect Cables. Order Lens separately.)

Camera only may be ordered.

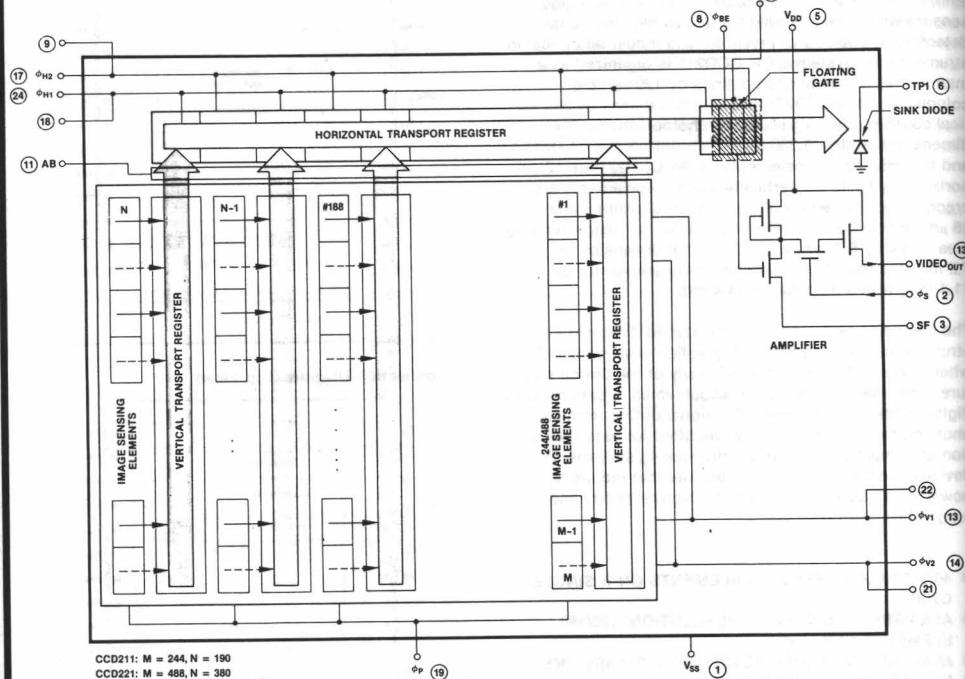

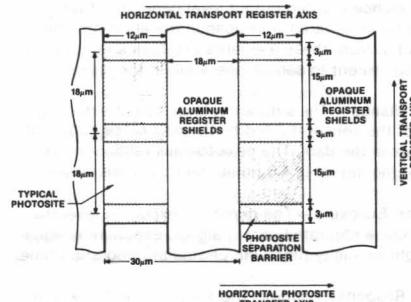

## Area Image Sensors

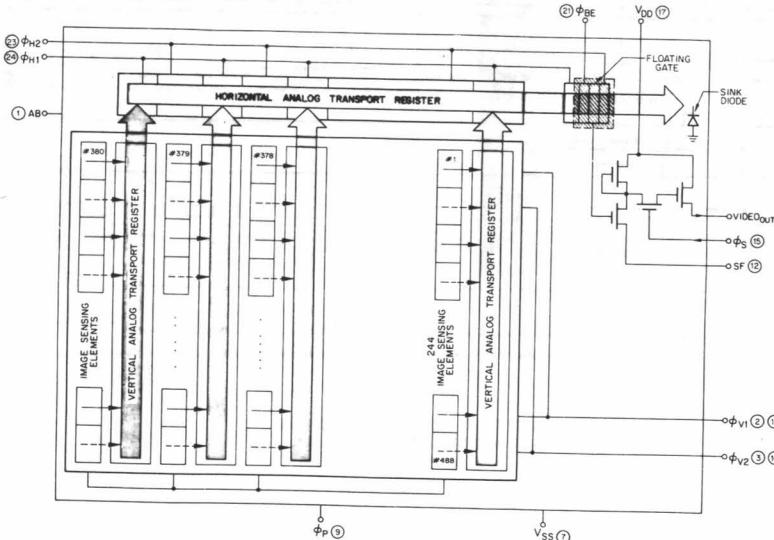

Area arrays are similar to the line scan sensors except that the photosites are arranged in a matrix format and the opaque transport registers are located between the photosite columns. The charge packets are transferred to the output amplifier in two separate fields, line by line. This technique is called the interline transfer approach.

The preceding tables summarize the features of Fairchild's Area Imaging Products. The CCD221, 488 x 380 element sensor, when operated at a 7.16 MHz horizontal clock frequency, provides a video output signal which is compatible with NTSC black and white television standards. The CCD211, 244 x 190 element sensor

can fill 25% of the area of a standard television monitor with NTSC resolution imagery or it can be used with a non-standard television CRT display.

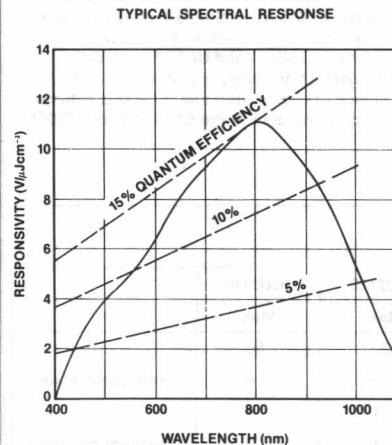

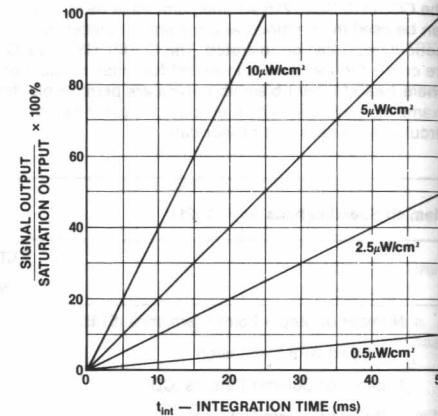

The highly precise location of the photosites allows precise identification of each component of the image signal, an important feature for applications requiring exact dimensional measurements. The devices are also well suited for use in video cameras that require low power, small size, high sensitivity and high reliability.

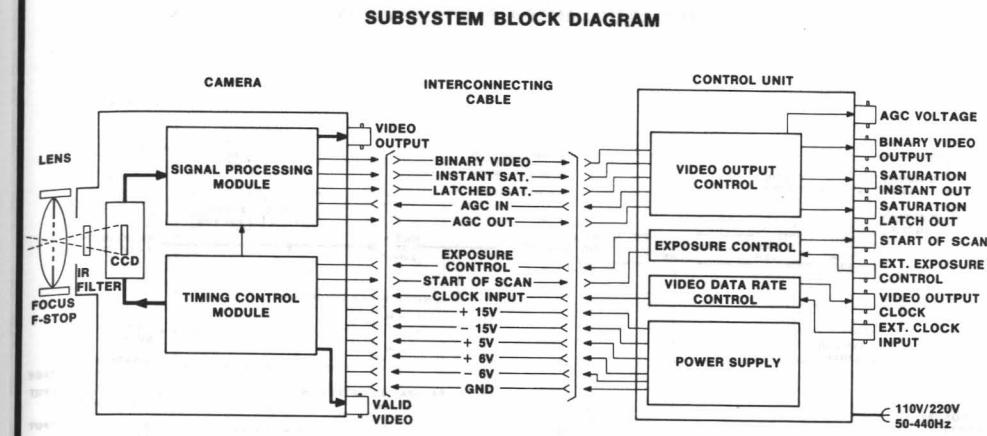

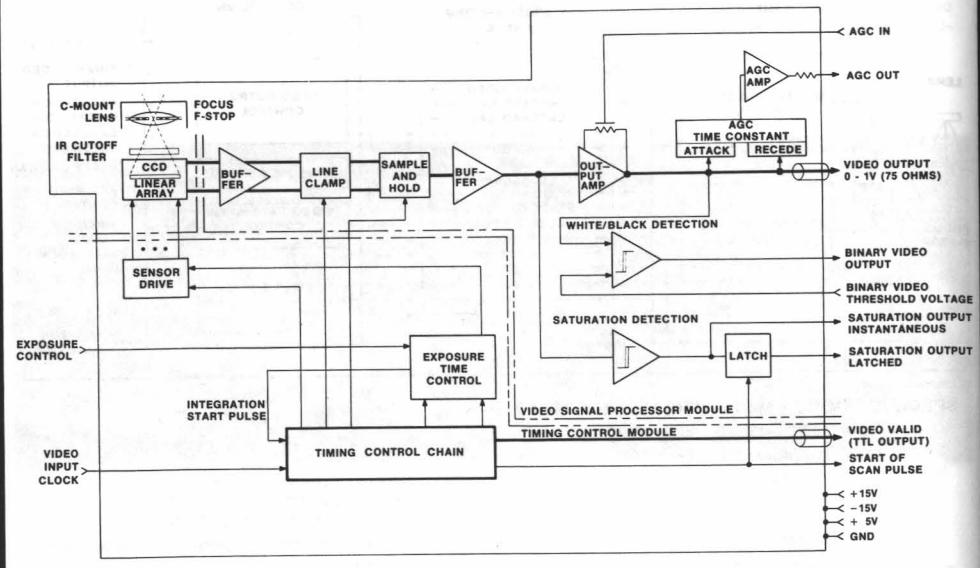

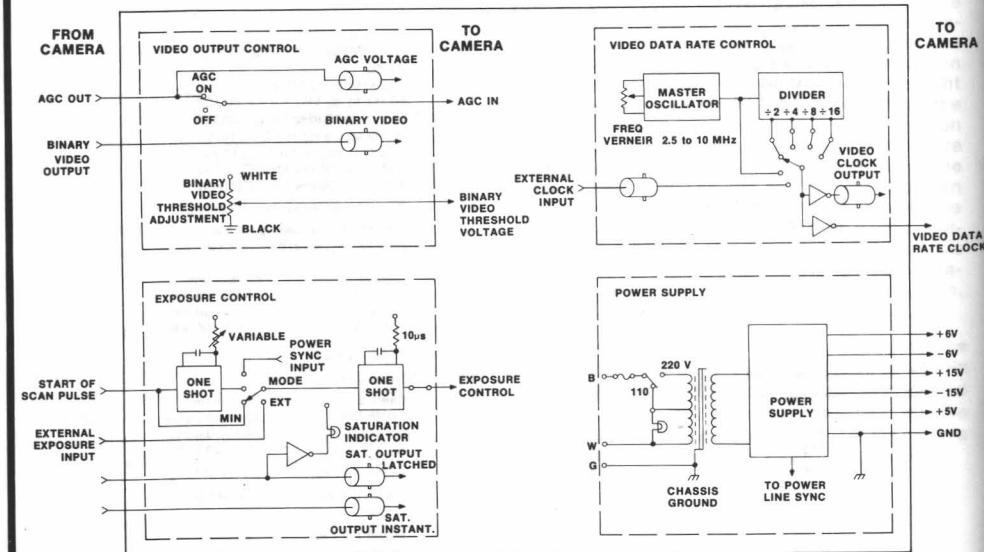

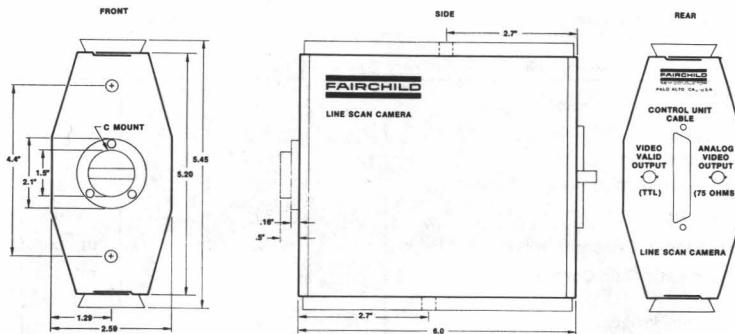

## Camera Subsystems

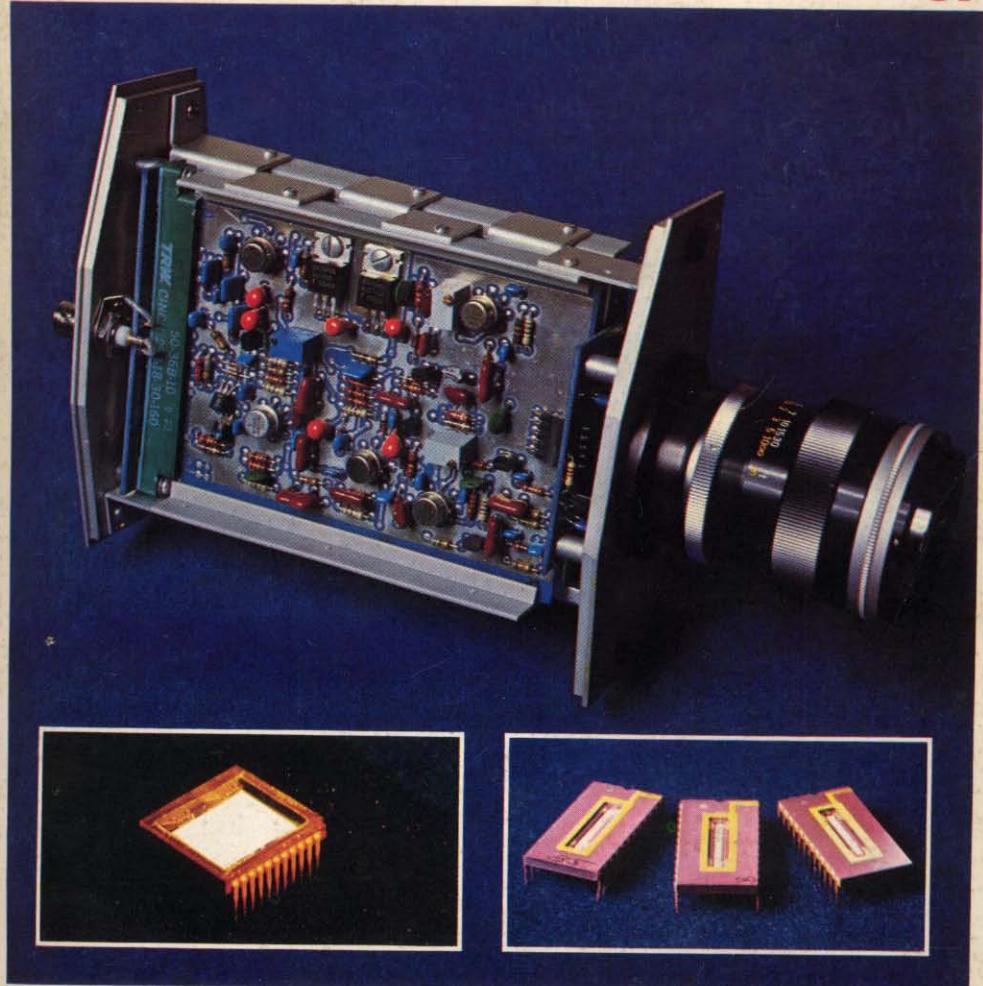

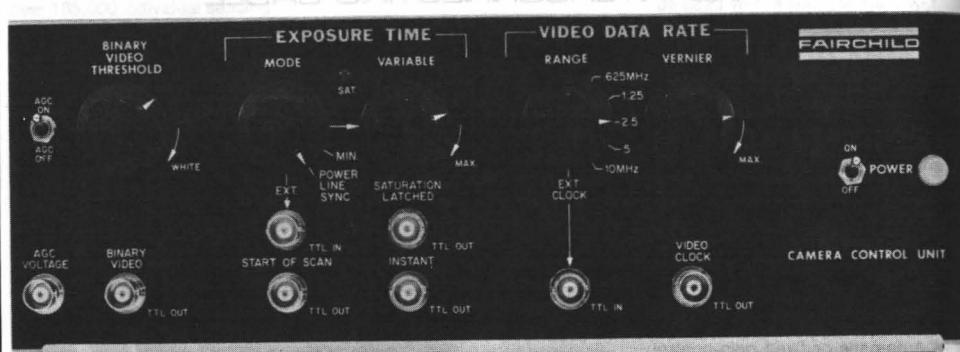

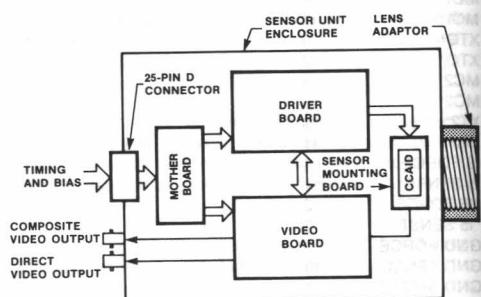

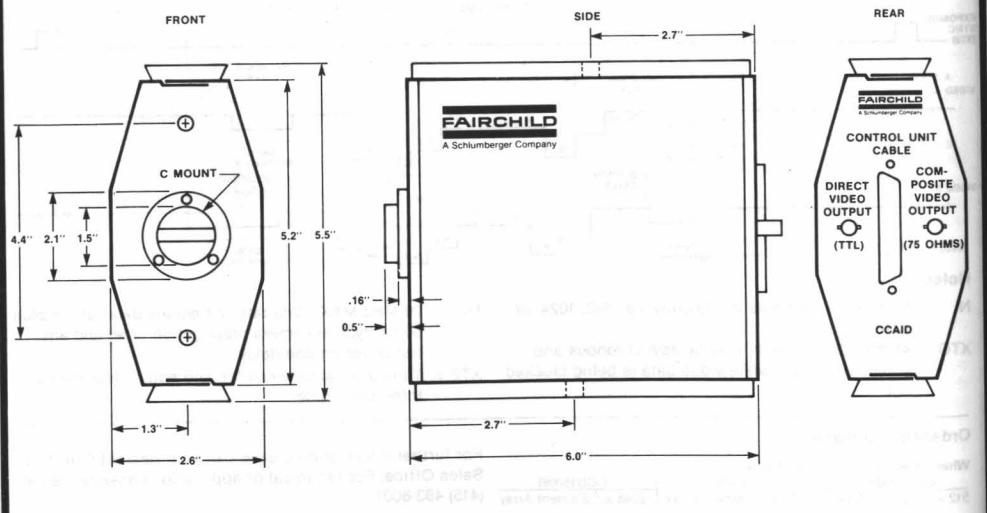

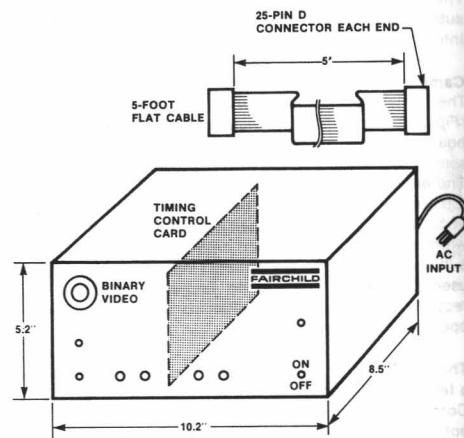

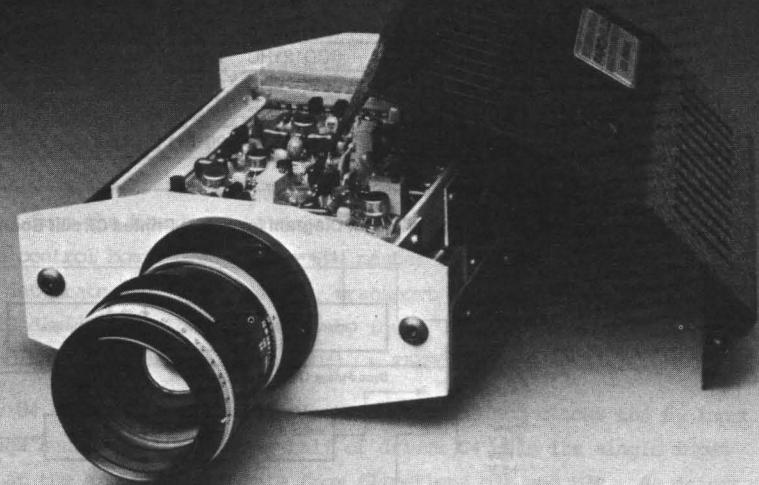

Fairchild CCD camera subsystems are fully assembled and calibrated electro-optical instruments useful in a wide variety of scientific and industrial applications.

Each subsystem is comprised of a camera, a line-powered control unit, and interconnecting cables. The camera, which may be ordered separately, may be equipped with a lens suitable for the application.

**Line Scan Camera** resolutions of 256, 512, 1024, 1728 and 2048 elements per line are available. Line scan subsystems are particularly useful for acquisition of optical data for objects in motion, i.e., facsimile scanning of documents transported past the camera's field of view or measurement of objects carried past a camera inspection station on a conveyor belt. Typical subsystem applications include microfiche and microfilm scanning, document scanning for mark sensing, facsimile transduction and OCR data acquisition; precision non-contact measurement and inspection, flaw detection,

shape analysis, dimensional measurement, color sorting; and for a wide variety of laboratory uses.

**Area Camera** resolutions of 244x190 elements and 488x380 elements per frame are offered. Additionally, a variety of optional accessories for use with the area subsystems are available.

Area scan subsystems are useful for acquisition of complete two-dimensional gray scale images of viewed objects. The CCD2000, when operating at a 7.16 MHz video data rate, is fully compatible with NTSC black and white television standards.

In addition to their obvious applications for television-type cameras, the area camera subsystems can be used for laboratory and industrial applications where two-dimensional image sensing is advantageous. Example applications include surveillance systems with MTI, industrial inspection in hostile environments, laser beam location and robotics.

| Ordering Code | For Use With      | Description                           |

|---------------|-------------------|---------------------------------------|

| LENS13C       | All               | 13 mm Lens, Standard C Mount          |

| LENS25C       | All               | 25 mm Lens, Standard C Mount          |

| LENS50C       | All               | 50 mm Lens, Standard C Mount          |

| LENS75C       | All               | 75 mm Lens, Standard C Mount          |

| CNTRLINE      | Line Scan Cameras | Control Unit with Interconnect Cables |

| CNTRAREA      | Area Cameras      | Control Unit with Interconnect Cables |

| CABLE         | All               | Interconnect Cables Only              |

| PIX1100       | CCD1100C          | Pixel Locator                         |

| PIX1200       | CCD1200C          | Pixel Locator                         |

| PIX1300       | CCD1300C          | Pixel Locator                         |

| PIX1400       | CCD1400C          | Pixel Locator                         |

| PIX1500       | CCD1500C          | Pixel Locator                         |

| PIX2000       | CCD2000C          | Pixel Locator                         |

| PIX2100       | CCD2100C          | Pixel Locator                         |

| REMOKIT       | Area Cameras      | Remote Sensor Kit                     |

| ADDBUFF       | Area Cameras      | Address Buffer Board                  |

| SWEEP         | Area Cameras      | Sweep Generator Board                 |

| MONITOR       | CCD2000C          | NTSC Monitor, Black and White         |

| 211KIT        | CCD2000C          | Conversion Kit                        |

| 221KIT        | CCD2100C          | Conversion Kit                        |

Camera Accessories

## Signal Processing

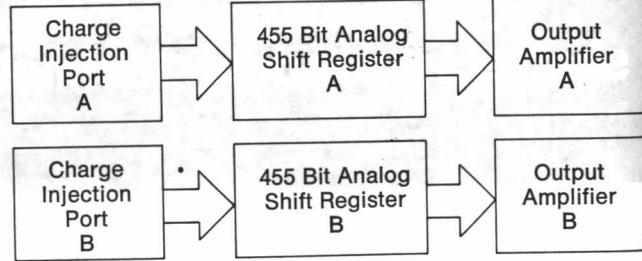

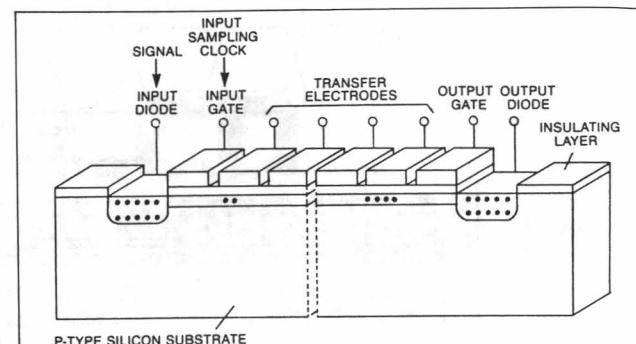

The capability to manipulate information in the form of discrete charge packets makes CCD technology ideal for analog signal processing. Fairchild signal processing components are monolithic silicon structures comprised of CCD analog shift registers, charge injection ports, and output charge-sensing amplifiers. They can be advantageously used for delay and temporary storage of analog video signals. The time delay for data transit through the CCD register is precisely controlled by the frequency of the externally supplied transport clock signal. Fairchild signal processing components include a sample-and-hold signal output stage for ease of application.

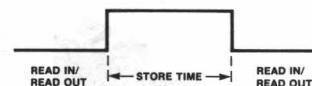

Fairchild video delay modules are printed circuit board structures which include the CCD321A2 device and are sold as fully assembled and calibrated units. The module is equipped for use as a variable delay circuit, using either an externally supplied or internal variable frequency clock, or for temporary analog data storage in a stopped-clock mode.

Typical applications for the CCD signal processing components and modules include time base correction for video tape recorders, fast input-slow output data expansion systems for A-D converter systems, comb filter realizations, drop-out compensators, and other analog applications up to frequencies of 30 MHz data rate.

| Ordering Code | Description                                |

|---------------|--------------------------------------------|

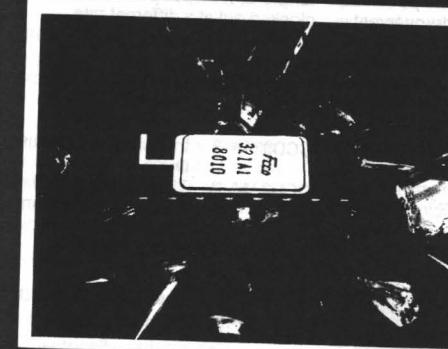

| CCD321A1      | Broadcast Video Delay Line                 |

| CCD321A2      | Industrial Video Delay Line                |

| CCD321A3      | Time Base Video Delay Line                 |

| CCD321A4      | Audio Delay Line                           |

| CCD321VM      | Video Module, Includes the CCD321A2 Device |

Signal Processing Products

*During the 70's Fairchild led the development of CCD Technology. Since the beginning, the buried-channel concept has been utilized in all CCD products. The product line therefore exhibits all the advantages of buried-channel technology including low noise, high speed and high density.*

*Transferring this process from an R&D to a volume production environment required extensive efforts in research, design, development and production engineering. Fairchild is the CCD industry leader.*

*The effort is still continuing... The 2048 x 1 is the longest device ever manufactured in high volume, the 488 x 380 is the largest chip on the market, and the CCD321 delay line is the fastest.*

*At Fairchild, CCD products are not an R&D curiosity or products looking for applications. They are here today and here to stay. The 1980's is the CCD Decade... call FAIRCHILD.*

*For further information on Fairchild CCD Imaging and Signal Processing products, call your nearest Fairchild Sales Office, representative or distributor.*

*For technical or applications information and assistance, call (415) 493-8001, (TWX 910-373-1227) or write Fairchild CCD Imaging, 4001 Miranda Avenue, Palo Alto, California 94304.*

**FAIRCHILD**

A Schlumberger Company

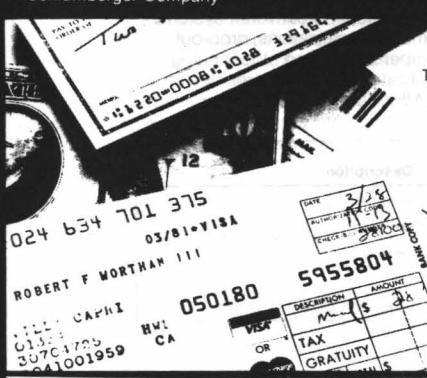

### Faster, better OCR data acquisition.

Thanks to our new CCD line-scan devices, you can read, sort, translate and log documents of any kind easier and faster than ever before. Fairchild is making it possible for manufacturers to upgrade their automated document-handling systems. In areas like credit card sales, drafts, check, currency and mail sorting. And other applications where scanners are being used to translate data from paper to computer memory, without human intervention. The result: A savings of both time and money. We can offer the sensing devices alone, with anywhere from 256 to 2,048 sense-elements. Or, we can provide an entire camera subsystem. We'd like to save you money where it counts. In your business. For further information, call or write CCD Imaging, Fairchild Advanced Technology Group, 4001 Miranda Avenue, Palo Alto, California 94304. Telephone: (415) 493-8001. TWX: 910-373-1227. Fairchild Camera and Instrument Corp.

## Our CCD device is saving you money where it counts.

Today's business environment demands more automation and more efficiency. And that means more opportunities for Fairchild's CCD line-scan cameras. Our cameras are designed to handle a wide variety of applications, from document handling to medical imaging. And they're built to last. So if you're looking for a reliable, cost-effective solution to your imaging needs, look no further than Fairchild.

For more information, contact us at (415) 493-8001. Or write to: Fairchild Advanced Technology Group, 4001 Miranda Avenue, Palo Alto, California 94304. We'll be happy to help you get started on your journey to a more efficient business environment.

## CCD 111 256-Element Line Scan Image Sensor

### CCD Imaging

#### Description

The CCD111 is a monolithic 256-element line image sensor. The device is designed for optical character recognition and other imaging applications that require high sensitivity and high speed. The CCD111 is pin-for-pin compatible with and a functional replacement for the CCD110F.

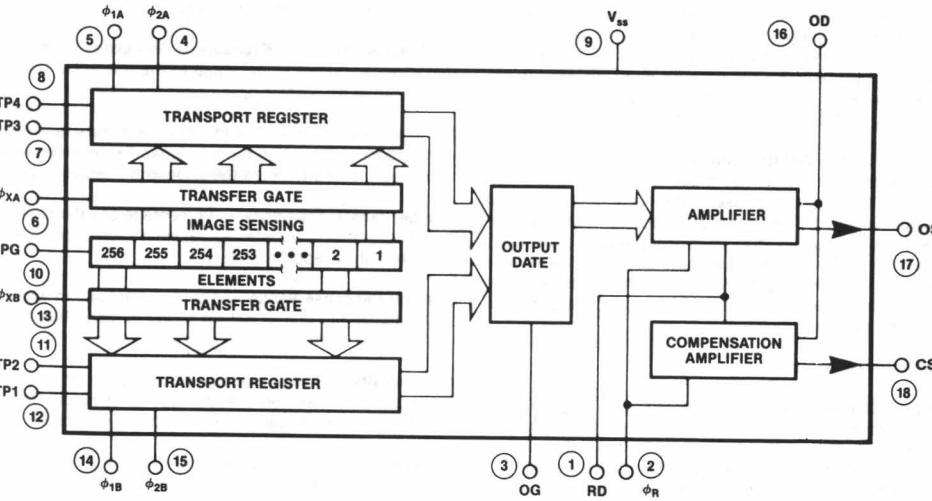

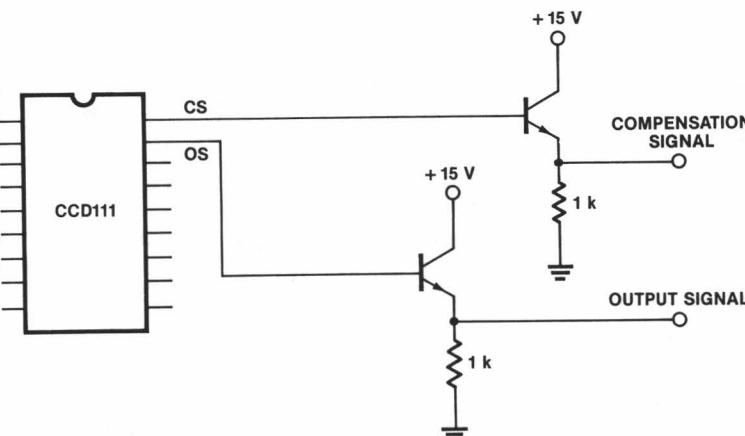

In addition to a line of 256 sensing elements, the CCD111 chip includes: two charge transfer gates, two 2-phase analog transport shift registers, an output charge detector/amplifier, and a compensation amplifier. The transport registers both feed the input of the charge detector resulting in sequential reading of the 256 sensing elements.

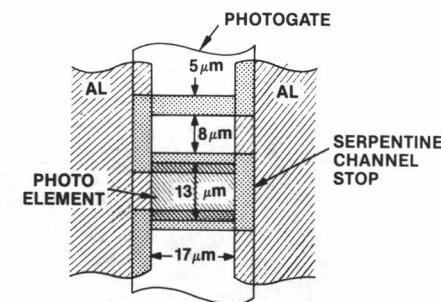

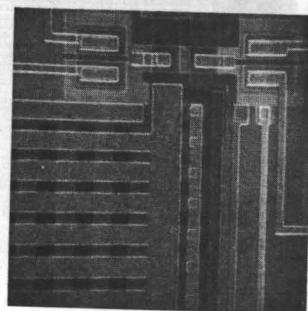

The cell size is 13  $\mu\text{m}$  (0.51 mils) by 17  $\mu\text{m}$  (0.67 mils) on 13  $\mu\text{m}$  (0.51 mils) centers. The device is manufactured using Fairchild advanced charge-coupled device n-channel Isoplanar buried-channel technology.

- DYNAMIC RANGE TYPICAL: 2500:1

- ON-CHIP VIDEO AND COMPENSATION AMPLIFIERS

- LOW POWER REQUIREMENTS

- ALL OPERATING VOLTAGES 15V AND UNDER

- LOW NOISE EQUIVALENT EXPOSURE

- DIMENSIONALLY PRECISE PHOTOSITE SPACING

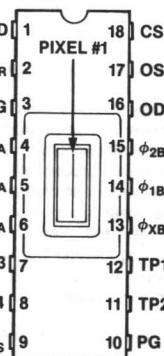

#### Connection Diagram

DIP (TOP VIEW)

| Pin Names:             | Pin Names:          |

|------------------------|---------------------|

| PG                     | Photogate           |

| $\phi_{XA}, \phi_{XB}$ | Transfer Clock      |

| $\phi_{1A}, \phi_{2A}$ | Transport Clocks    |

| $\phi_{1B}, \phi_{2B}$ | OG                  |

| OG                     | OS                  |

| OS                     | OD                  |

| OD                     | Compensation Source |

| CS                     | $\phi_R$            |

| $\phi_R$               | RD                  |

| RD                     | TP                  |

| TP                     | V <sub>ss</sub>     |

| V <sub>ss</sub>        |                     |

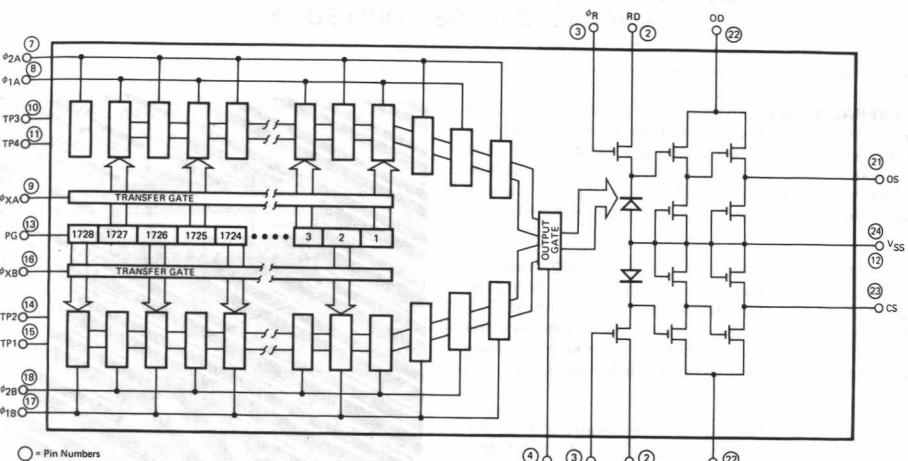

#### Block Diagram

## CCD111

**Functional Description**

The CCD111 consists of the following functional elements illustrated in the Block Diagram:

**Image Sensor Elements** — A row of 256 image sensor elements separated by a diffused channel stop and covered by a silicon photogate. Image photons pass through the transparent polycrystalline silicon photogate and are absorbed in the single crystal silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

**Two Transfer Gates** — Gate structures adjacent to the row of image sensor elements. The charge packets accumulated in the image sensor elements are transferred out via the transfer gates to the transport registers whenever the transfer gate voltages go HIGH. Alternate charge packets are transferred to the left and right transport registers. The transfer gates also control the integration time for the sensing elements.

**Two 130-Bit Analog Transport Shift Registers** — One on each side of the line of image sensor elements and are separated from it by a transfer gate. The two registers, called the transport registers, are used to move the light generated charge packets delivered by the transfer gates serially to the charge detector/amplifier. The complementary phase relationship of the last elements of the two transport registers provides for alternate delivery of charge packets to establish the original serial sequence of the line of video in the output circuit.

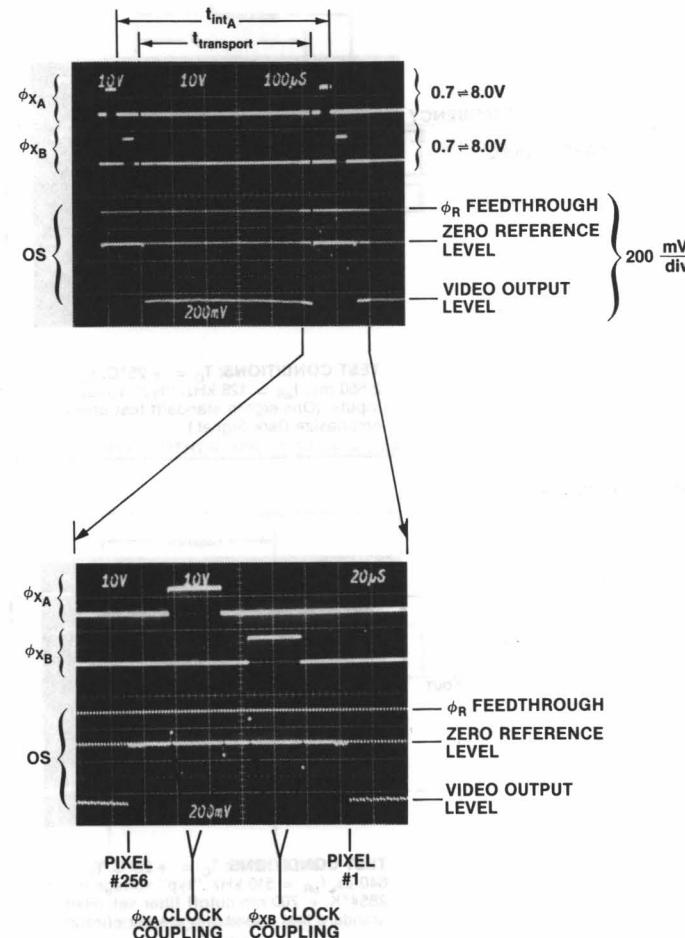

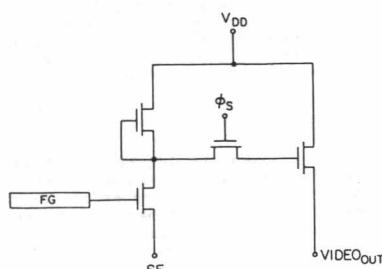

**A Gated Charge Detector/Amplifier** — Charge packets are transported to a precharged diode whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of the output n-channel MOS transistor producing a signal at the output OS. A reset transistor is driven by the reset clock ( $\phi_R$ ) and recharges the charge detector diode capacitance before the arrival of each new signal charge packet from the transport registers.

**Definition of Terms**

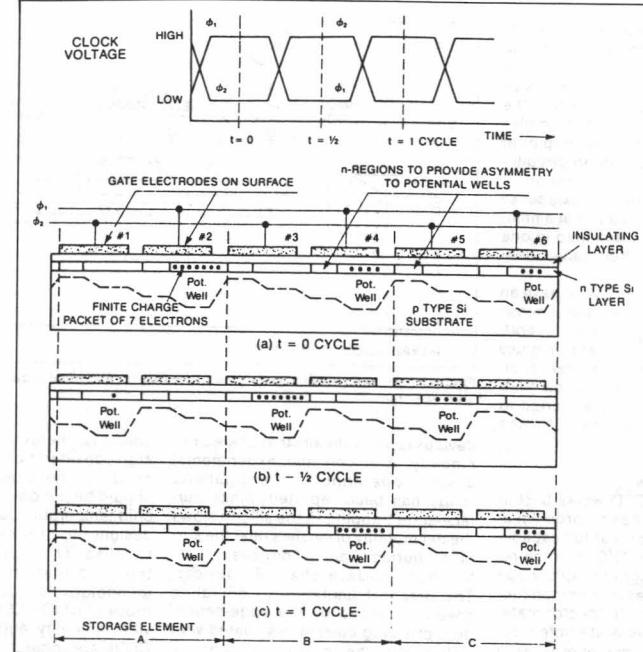

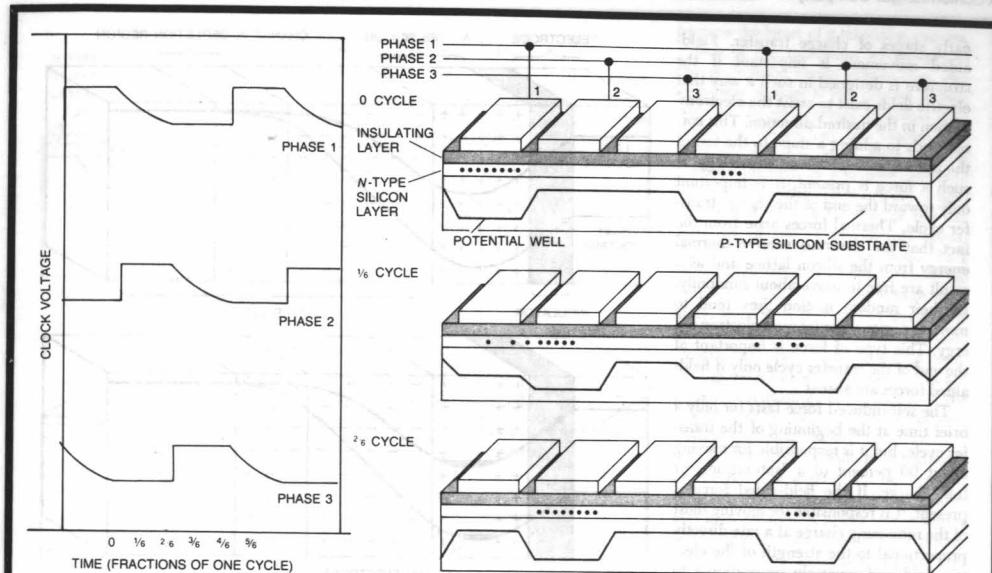

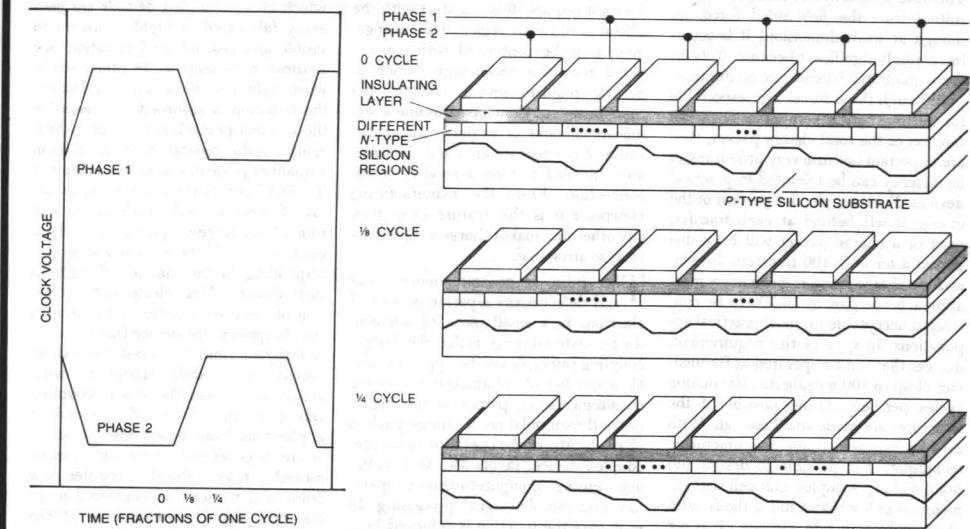

**Charge-Coupled Device** — A charge-coupled device is a semiconductor device in which finite isolated charge packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge packets

are minority carriers with respect to the semiconductor substrate.

**Transfer Clocks  $\phi_{XA}, \phi_{XB}$**  — The voltage waveforms applied to the transfer gates to move the accumulated charge from the image sensor elements to the CCD transport registers.

**Transport Clocks  $\phi_{1A}, \phi_{2A}, \phi_{1B}, \phi_{2B}$**  — The two sets of 2-phase waveforms applied to the gates of the transport registers to move the charge packets received from the image sensor elements to the gated charge detector/amplifier.

**Gated Charge Detector/Amplifier** — The output circuit of the CCD111 that receives the charge packets from the transport registers and provides a signal voltage proportional to the size of each charge packet received. Before each new charge packet is sensed, a reset clock returns the charge detector voltage to a fixed level.

**Reset Clock  $\phi_R$**  — The voltage waveform required to reset the voltage on the charge detector.

**Dynamic Range** — The saturation exposure divided by the rms noise equivalent exposure. (This does not take into account dark signal components.) Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times rms noise.

**RMS Noise Equivalent Exposure** — The exposure level that gives an output signal equal to the rms noise level at the output in the dark.

**Saturation Exposure** — The minimum exposure level that will produce a saturation output signal. Exposure is equal to the light intensity times the photosite integration time.

**Charge Transfer Efficiency** — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

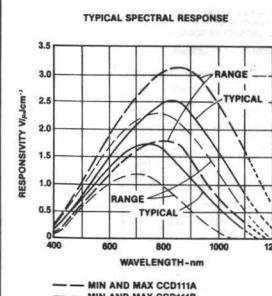

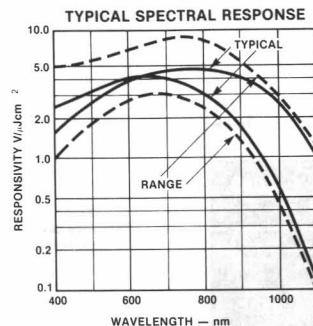

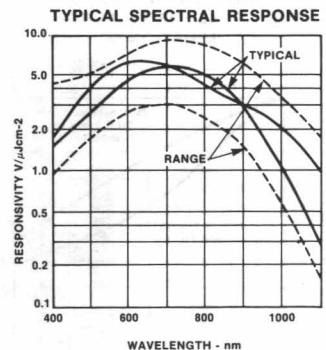

**Spectral Response Range** — The spectral band in which the response per unit of radiant power is more than 10% of the peak response.

**Responsivity** — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

**Total Photoresponse Non-uniformity** — The difference of the response levels of the most and the least sensitive

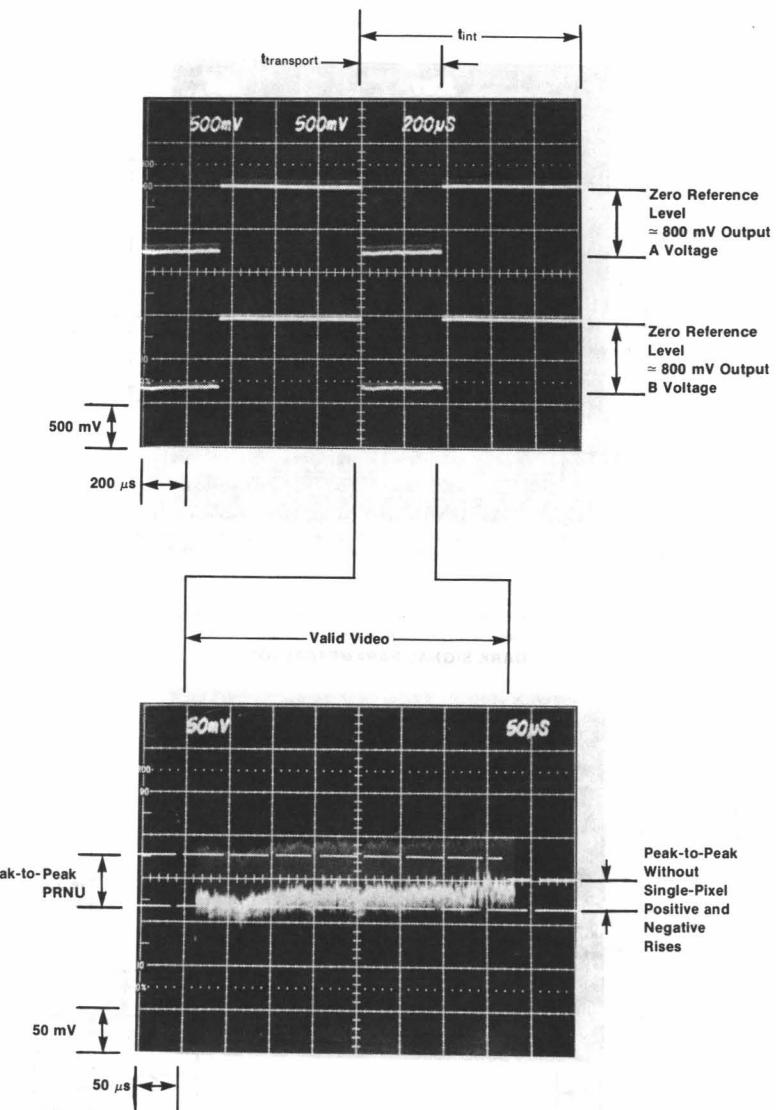

## CCD111

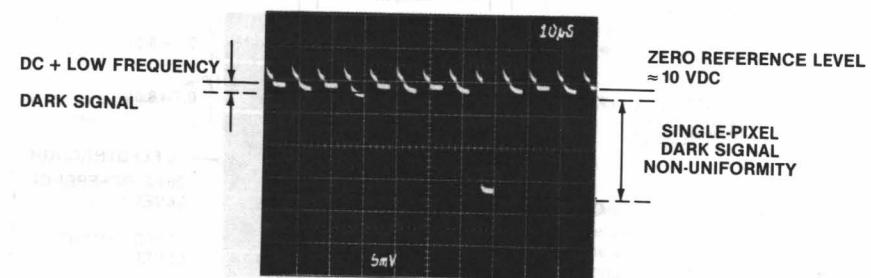

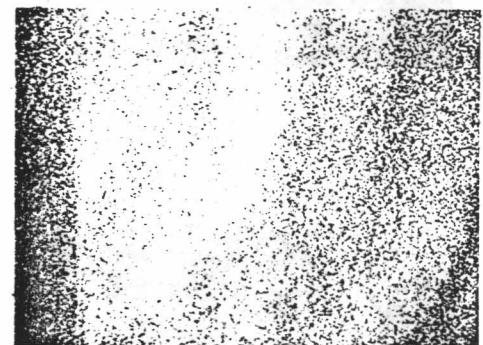

element under uniform illumination. Measurement of PRNU excludes first and last elements. (See accompanying photos for details of definition.)

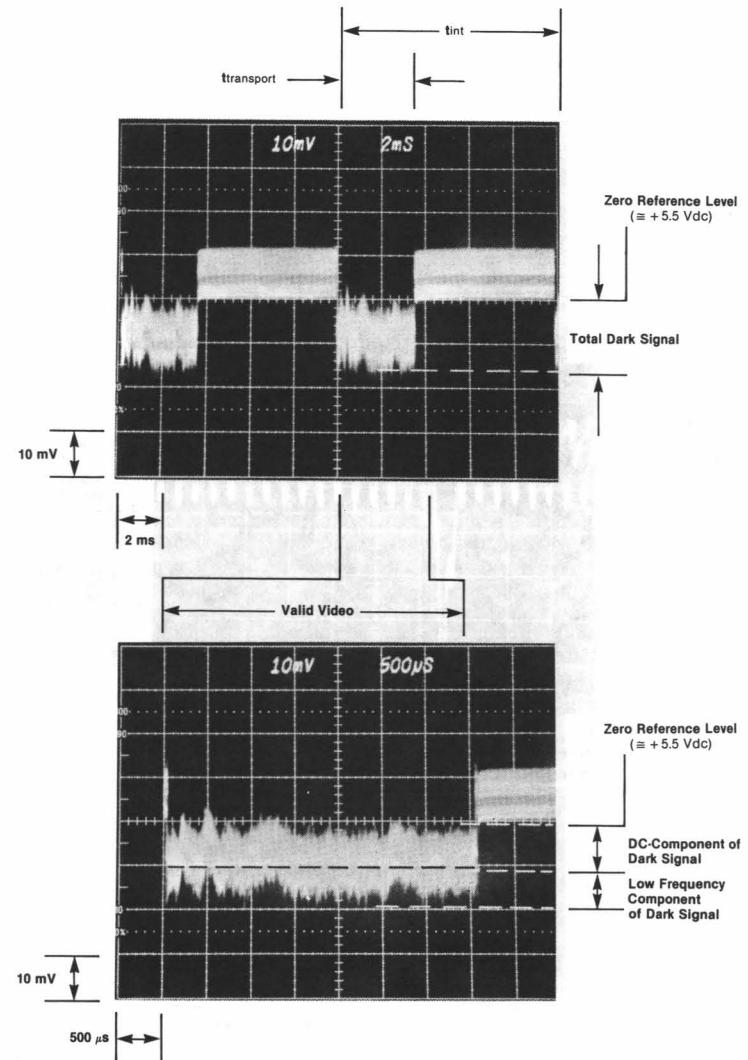

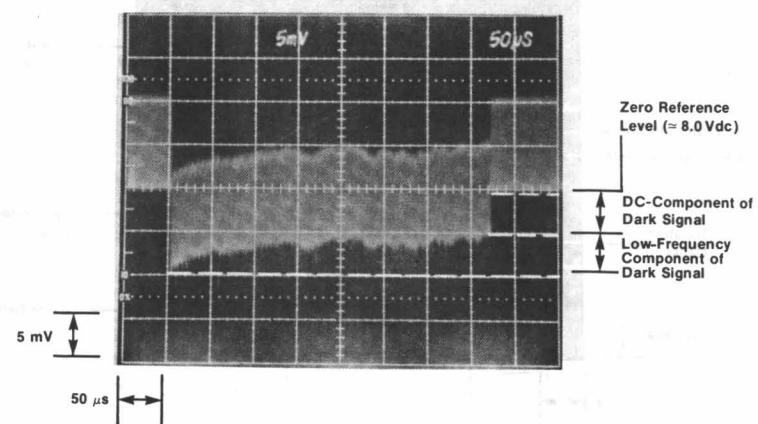

**Dark Signal** — The output signal in the dark caused by thermally generated electrons that is a linear function of the integration time and highly sensitive to temperature. (See accompanying photos for details of definition.)

**Saturation Output Voltage** — The maximum useable signal output voltage. Charge transfer efficiency decreases sharply when the saturation output voltage is exceeded.

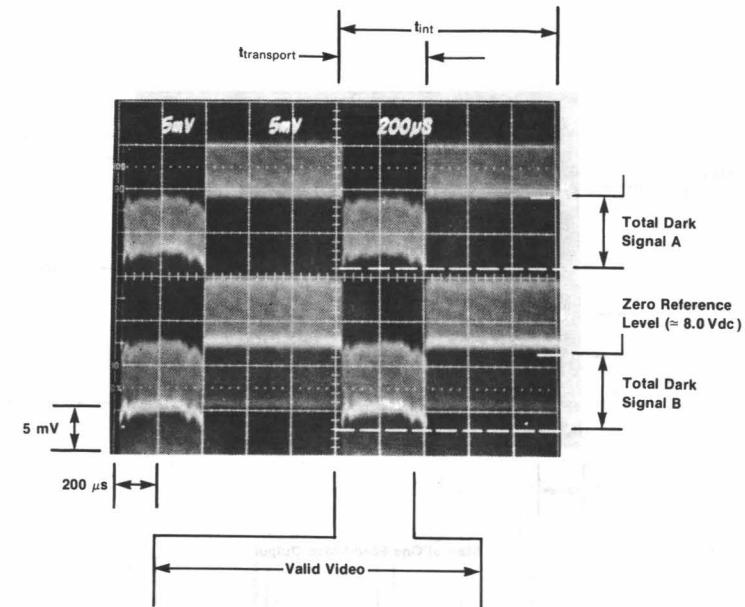

**Integration Time** — The time interval between the falling edges of any two transfer pulses  $\phi_{XA}$  or  $\phi_{XB}$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

**Pixel** — A picture element (photosite).

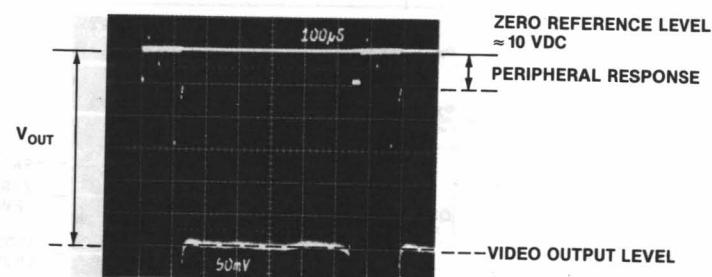

**Peripheral Response** — The output signal caused by light-generated charge that is collected by the transport registers (instead of the photosites). The device is covered, except over the photosites, by a gapped metal layer, which functions both as an array of interconnections and as a reflective light shield. The major component of Peripheral Response for visible light ( $\lambda \leq 700\text{nm}$ ) is generated in the transport registers by light transmitted through these gaps in the metal above the registers. For near-infrared light ( $\lambda \geq 700\text{nm}$ ), especially on CCD111A devices, a portion of the charge generated by light absorbed under the photosites and one transport register is collected in the opposite transport register.

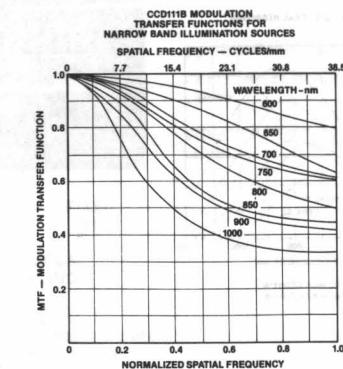

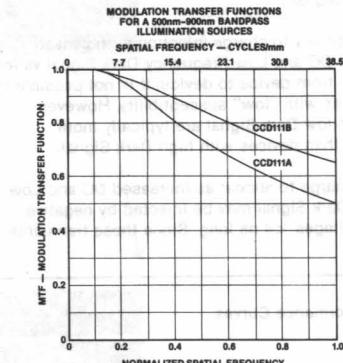

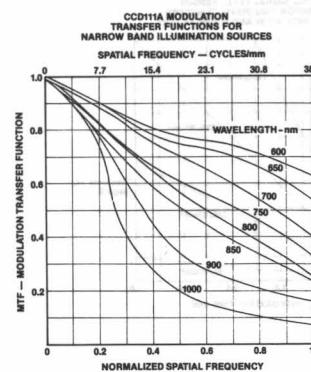

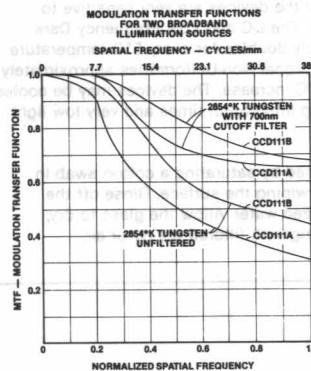

**Major Differences Between the CCD111A and CCD111B** — Both the CCD111A and the CCD111B have the same responsivity to visible light (400-700nm). The principal

**DC Characteristics:  $T_c = 25^\circ\text{C}$  (Note 1)**

| Symbol   | Characteristic                  | Limits |      |      | Unit | Condition |

|----------|---------------------------------|--------|------|------|------|-----------|

|          |                                 | Min    | Typ  | Max  |      |           |

| $V_{OD}$ | Output Transistor Drain Voltage | 14.5   | 15.0 | 15.5 | V    |           |

| $V_{RD}$ | Reset Transistor Drain Voltage  | 11.5   | 12.0 | 12.5 | V    |           |

| $V_{OG}$ | Output Gate Voltage             |        | 5.0  |      | V    |           |

| $V_{PG}$ | Photogate Voltage               | 9.5    | 10.0 | 12.5 | V    |           |

| TP1, TP3 | Test Points                     |        | 0.0  |      | V    |           |

| TP2, TP4 | Test Points                     | 14.5   | 15.0 | 15.5 | V    |           |

differences are as follows:

The CCD111A is intended for use in applications where very low dark signal and high responsivity to very near-infrared (700-900nm) light are needed, and where peripheral response is not critical.

The CCD111B is selected for use in applications where standard responsivity to very near-infrared (700-900nm) light and standard dark signal are acceptable and where peripheral response needs to be minimized.

It is not recommended that either part be used with illumination containing wavelengths greater than 900nm (near-infrared). If use of such a light source (unfiltered tungsten, for example) is unavoidable, the CCD111B will generally provide the user with more satisfactory results. The table on performance characteristics provides more information.

**Absolute Maximum Ratings**

|                                              |                                  |

|----------------------------------------------|----------------------------------|

| Storage Temperature                          | -25°C to 100°C                   |

| Operating Temperature                        | -25°C to 55°C                    |

| Pins 2, 3, 4, 5, 6, 7, 10,<br>12, 13, 14, 15 |                                  |

| Pins 1, 8, 11, 16                            | -0.3V to 15V                     |

| Pins 17, 18                                  | -0.3V to 18V                     |

| Pin 9                                        | output, no voltage applied<br>OV |

**Caution Note**

This device has limited built-in gate protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins OS and CS to  $V_{SS}$  or  $V_{OD}$  during operation of the device. Shorting these pins temporarily to  $V_{SS}$  or  $V_{OD}$  may destroy the output amplifiers.

**CCD111**

Clock Characteristics:  $T_c = 25^\circ\text{C}$  (Note 1)

| Symbol                                                   | Characteristic                                   | Limits |      |     | Unit | Condition  |

|----------------------------------------------------------|--------------------------------------------------|--------|------|-----|------|------------|

|                                                          |                                                  | Min    | Typ  | Max |      |            |

| $V_{\phi1AL}, V_{\phi1BL}$<br>$V_{\phi2AL}, V_{\phi2BL}$ | Transport Clocks LOW                             | 0.0    | 0.5  | 0.8 | V    | Note 2     |

| $V_{\phi1AH}, V_{\phi1BH}$<br>$V_{\phi2AH}, V_{\phi2BH}$ | Transport Clocks HIGH                            | 7.5    | 8.0  | 8.5 | V    | Note 5     |

| $V_{\phiXAL}, V_{\phiXB1}$                               | Transfer Clock LOW                               | 0.0    | 0.5  | 0.8 | V    | Notes 2, 5 |

| $V_{\phiXA1}, V_{\phiXB1}$                               | Transfer Clock HIGH                              | 7.5    | 8.0  | 8.5 | V    | Note 5     |

| $V_{\phiRL}$                                             | Reset Clock LOW                                  | 0.0    | 0.5  | 0.8 | V    | Notes 2, 5 |

| $V_{\phiRH}$                                             | Reset Clock HIGH                                 | 7.5    | 8.0  | 8.5 | V    | Notes 3, 5 |

| $f_{\phi1A}, f_{\phi1B}$<br>$f_{\phi2A}, f_{\phi2B}$     | Maximum Transport Clock Frequency                |        | 5.0  |     | MHz  | Note 5     |

| $f_{\phiR}$                                              | Maximum Reset Clock Frequency (Output Data Rate) |        | 10.0 |     | MHz  | Note 6     |

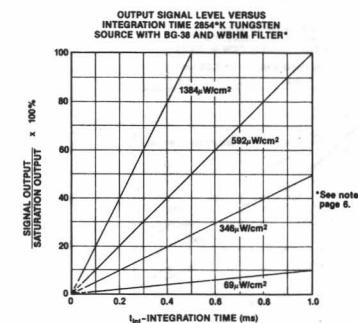

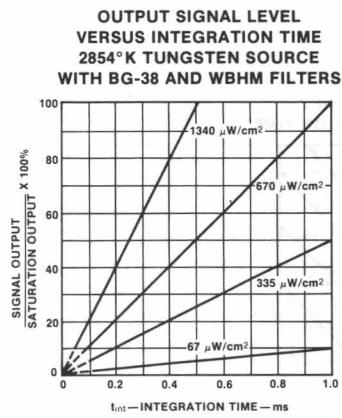

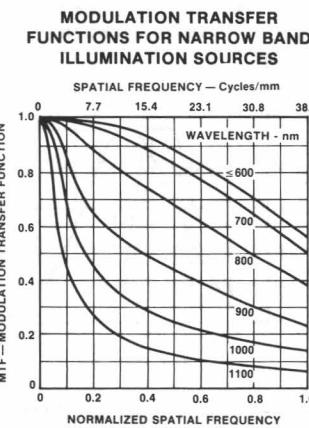

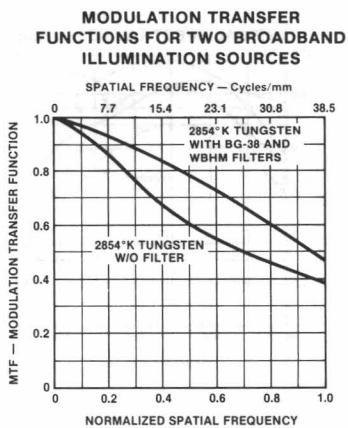

AC Characteristics:  $T_c = 25^\circ\text{C}$ ,  $f_{\phiR} = 1.0 \text{ MHz}$ ,  $t_{int} = 320 \mu\text{s}$ ,  $t_{transport} = 259 \mu\text{s}$ , Light Source =  $2854^\circ\text{K} + \text{filters as specified}$ . All operating voltages nominal specified values. (Note 1)

| Symbol | Parameter                                                                    | Range           |                    |     | Unit                      | Condition             |

|--------|------------------------------------------------------------------------------|-----------------|--------------------|-----|---------------------------|-----------------------|

|        |                                                                              | Min             | Typ                | Max |                           |                       |

| DR     | Dynamic Range<br>(relative to rms noise)<br>(relative to peak-to-peak noise) | 1250:1<br>250:1 | 2500:1<br>500:1    |     |                           | Note 7                |

| NEE    | RMS Noise<br>Equivalent Exposure                                             |                 | $2 \times 10^{-4}$ |     | $\mu\text{J}/\text{cm}^2$ |                       |

| SE     | Saturation Exposure                                                          |                 | 0.5                |     | $\mu\text{J}/\text{cm}^2$ |                       |

| CTE    | Charge Transfer Efficiency                                                   |                 | 99.995             |     | %                         | Note 8                |

| SR     | Spectral Response<br>Range Limits                                            |                 | 0.45 – 1.05        |     | $\mu\text{m}$             |                       |

| P      | Power Dissipation                                                            |                 | 100                |     | mW                        | $V_{OD} = 15\text{V}$ |

| Z      | Output Impedance                                                             |                 | 1000               |     | $\Omega$                  |                       |

| N      | RMS Noise<br>Peak-to-Peak Noise                                              |                 | 80<br>400          |     | $\mu\text{V}$             |                       |

**CCD111**

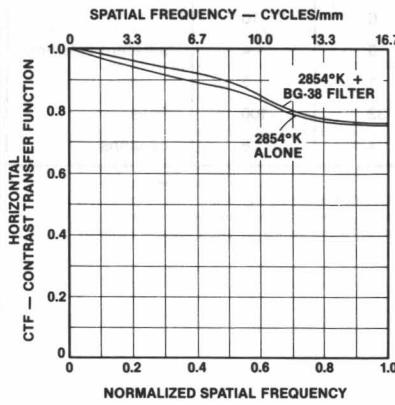

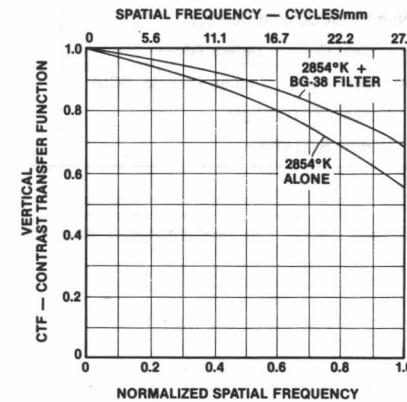

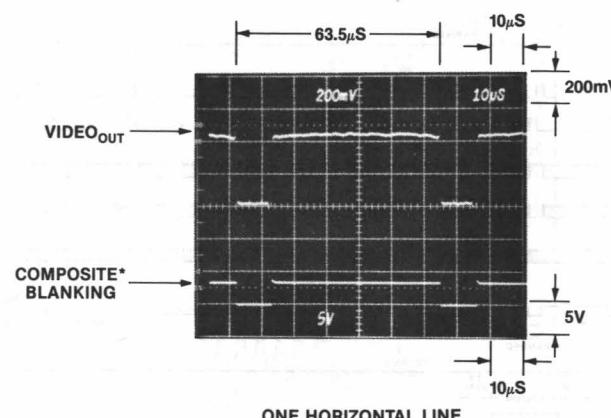

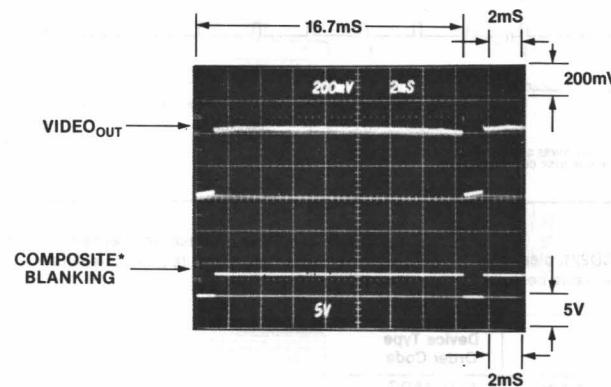

Performance Characteristics:  $T_c = 25^\circ\text{C}$ ,  $f_{\phiR} = 1.0 \text{ MHz}$ ,  $t_{int} = 320 \mu\text{s}$ ,  $t_{transport} = 259 \mu\text{s}$ ,

Light Source =  $2854^\circ\text{K} + \text{filters as specified}$ .

All operating voltages nominal specified values. (Note 1)

| Symbol    | Characteristic                            | Range   |     |     |         |     |                | Unit                               | Condition |

|-----------|-------------------------------------------|---------|-----|-----|---------|-----|----------------|------------------------------------|-----------|

|           |                                           | CCD111A |     |     | CCD111B |     |                |                                    |           |

| Min       | Typ                                       | Max     | Min | Typ | Max     |     |                |                                    |           |

| PRNU      | Photoresponse Non-uniformity Peak-to-Peak |         |     |     |         |     |                |                                    |           |

|           | 2854°K + 700 nm cutoff filter             | 35      | 70  |     | 25      | 70  | mV             | 14, 15, 16                         |           |

|           | 2854°K + 900 nm cutoff filter             | 45      | 110 |     | 45      | 110 | mV             | 14, 15, 16                         |           |

|           | 2854°K unfiltered                         | 70      |     |     | 60      |     | mV             | 14, 15, 16                         |           |

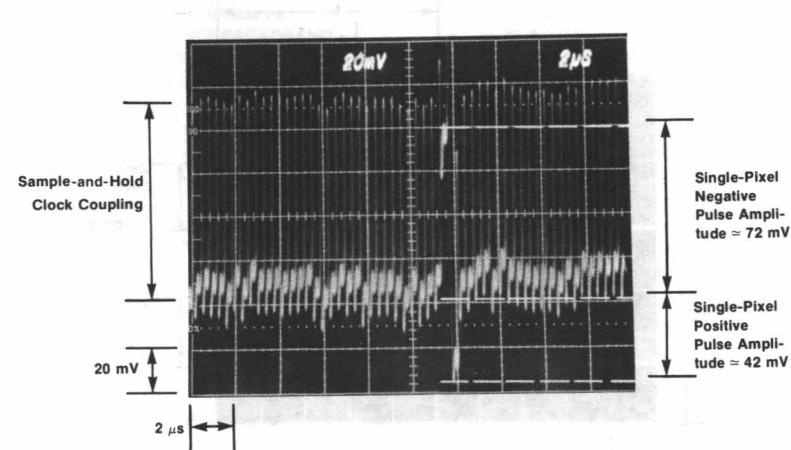

| RI        | Single-pixel Positive Pulses              | <10     |     |     | <10     |     | mV             | 15, 16                             |           |

|           | Single-pixel Negative Pulses              | 20      | 60  |     | 20      | 60  | mV             | 15, 16                             |           |

| DS        | Register Imbalance ('Odd'/'Even')         | <5      |     |     | <5      |     | mV             | 15, 16                             |           |

| SPDSNU    | Dark Signal DC Component                  | 0       | <1  | 3   | 0       | 2   | 15             | mV                                 | 2, 9, 10  |

|           | Low Frequency Component                   | 0       | <1  | 2   | 0       | 2   | 10             | mV                                 | 2, 9, 11  |

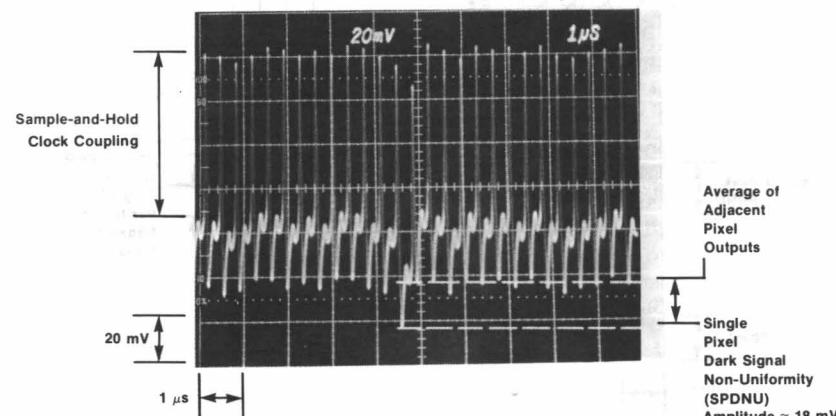

| PR        | Single-pixel DS Non-uniformity            | 0       | <1  | 2   | 0       | 1   | 2              | mV                                 | 9, 11, 12 |

|           | Peripheral Response                       |         |     |     |         |     |                |                                    |           |

|           | 2854°K + 700 nm cutoff filter             | 10      | 17  |     | <2      | 5   | % of $V_{OUT}$ | 14                                 |           |

|           | 2854°K + 900 nm cutoff filter             | 12      | 20  |     | 3       | 7   | % of $V_{OUT}$ | 14                                 |           |

| R         | 2854°K unfiltered                         | 25      |     |     | 4       |     | % of $V_{OUT}$ | 14                                 |           |

|           | Responsivity                              |         |     |     |         |     |                |                                    |           |

|           | 2854°K + 700 nm cutoff filter             | 0.7     | 1.3 | 2.1 | 0.5     | 1.1 | 2.0            | $\text{V}/\mu\text{J}/\text{cm}^2$ | 13, 14    |

|           | 2854°K + 900 nm cutoff filter             | 1.3     | 2.4 | 3.9 | 0.8     | 1.6 | 2.4            | $\text{V}/\mu\text{J}/\text{cm}^2$ | 13, 14    |

|           | 2854°K unfiltered                         |         |     |     | 2.0     |     | 0.9            | $\text{V}/\mu\text{J}/\text{cm}^2$ | 13, 14    |

| $V_{SAT}$ | Saturation Output Voltage                 | 500     | 900 |     | 500     | 900 | mV             |                                    | 17        |

Notes

- $T_c$  is defined as the package temperature, measured on the back surface of the ceramic body.

- Negative transients on any clock pin going below 0.0V may cause charge injection that results in an increase in the apparent Dark Signal.

- $V_{\phiRH}$  should track  $V_{RD}$ .

- The data output frequency  $f_{\phiR}$  is twice that of each transport clock ( $f_{\phi1A}, f_{\phi1B}, f_{\phi2A}, f_{\phi2B}$ ).

- $C_{\phiXA} = C_{\phiXB} = 20\text{pF}$ ,  $C_{\phi1A} = C_{\phi2A} = C_{\phi1B} = C_{\phi2B} = 32\text{pF}$ ,  $C_{\phiR} = 5\text{pF}$ .

- Minimum reset clock frequency is limited by the increase in Dark Signal.

- Dynamic Range is defined as " $V_{SAT}/\text{rms (temporal) Noise}$ " or " $V_{SAT}/\text{Peak-to-Peak (temporal) Noise}$ ".

- CTE is measured for a one-stage transfer.

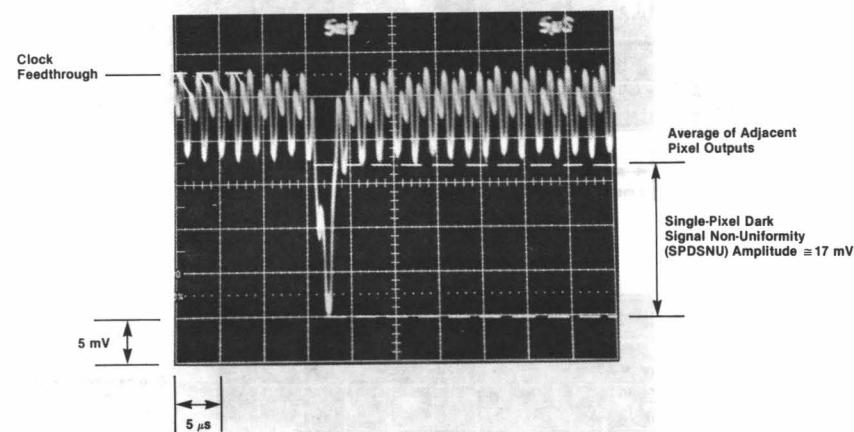

- See photographs for Dark Signal definitions.

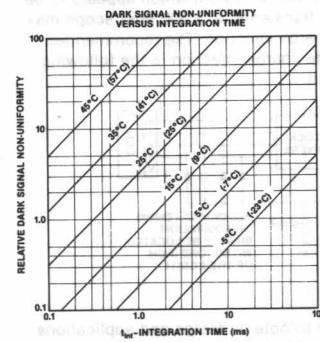

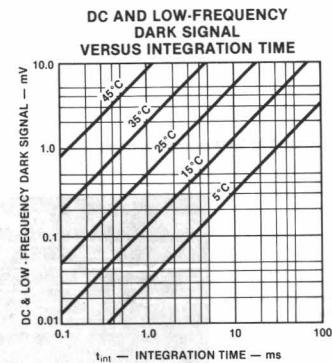

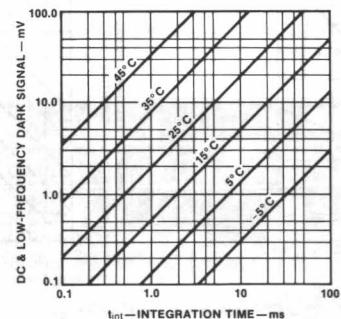

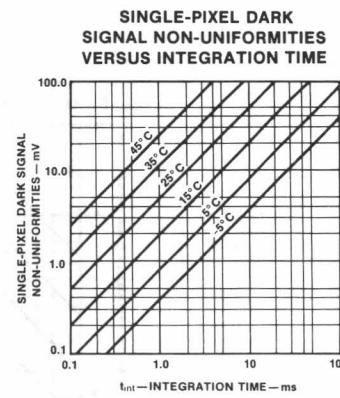

- DC and low-frequency Dark Signal components approximately double for every  $5^\circ\text{C}$  increase in  $T_c$ . The shift register component is also inversely proportional to  $T_c$ .

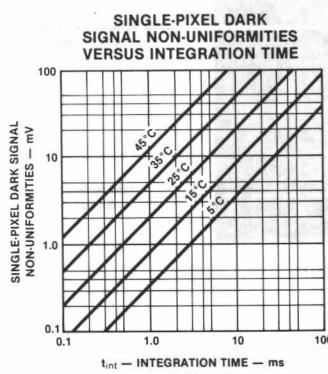

- Single-pixel Dark Signal non-uniformity (SPDSNU) approximately doubles for every  $8^\circ\text{C}$  increase in  $T_c$ . They are also directly proportional to the integration time  $t_{int}$ .

- Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU.

- RESPONSIVITY is defined as the "volts of video output" per "Incident Radiant Energy measured over the 350 nm-1200 nm band." The device will not respond to infrared wavelengths longer than  $\lambda > 1200 \text{ nm}$ . However, 2/3 of the radiant energy from a  $2854^\circ\text{K}$  source is at  $\lambda > 1200 \text{ nm}$ . For the unfiltered 2854°K source, the responsivity values for light measured over  $0 < \lambda < \infty$  will be  $\sim 0.3X$  of the responsivity values for light measured over 350 nm  $< \lambda < 1200 \text{ nm}$ .

## CCD111

## Notes (cont'd)

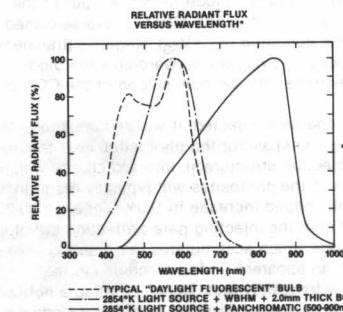

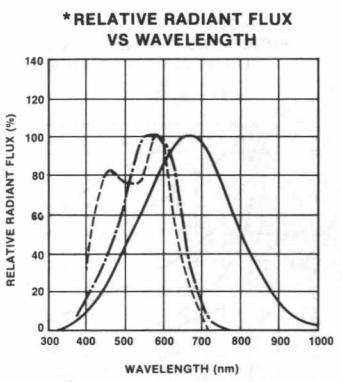

14. OPTICAL FILTERS: a "700 nm cutoff" filter is realized by using one "Wide Band Hot Mirror" (Optical Coating Labs, Inc., Santa Rosa, California) and one 2.0 mm thick "BG-38" blue glass (Schott Optical Glass, Duryea, Pennsylvania) filter in series. The "900 nm cutoff" filter is available on special order; consult Fairchild CCD Applications Engineering for details. Transmittance curves for the two cutoff filters and Spectral Energy Distribution curves for these filters with a 2854°K light source are given in the "Typical Performance Curves" section of this data sheet. It should be noted that the "2854°K + 700 nm cutoff" source is a good approximation to a Daylight Fluorescent bulb.

15. All PRNU measurements taken at a 350mV output level using a F5.0 lens; all PRNU measurements exclude the outputs from the first and last photoelements of the array. The "f" number is defined as the distance from the lens to the array divided by the diameter of the lens aperture. As f number increases, the resulting more highly collimated light causes package window aberrations to dominate and increase the PRNU. A lower f number ( $f \leq 5$ ) results in less collimated light, causing photosite blemishes to dominate PRNU.

16. See photographs for PRNU definitions.

17. See test load configuration.

## Test Load Configuration

## CCD111

## Photoelement Dimensions

ALL DIMENSIONS ARE TYPICAL VALUES.

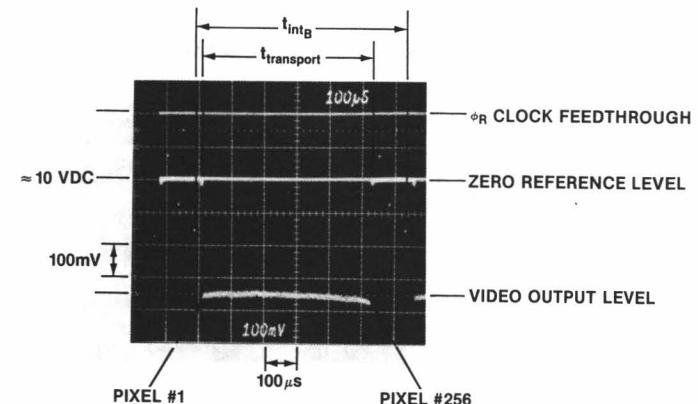

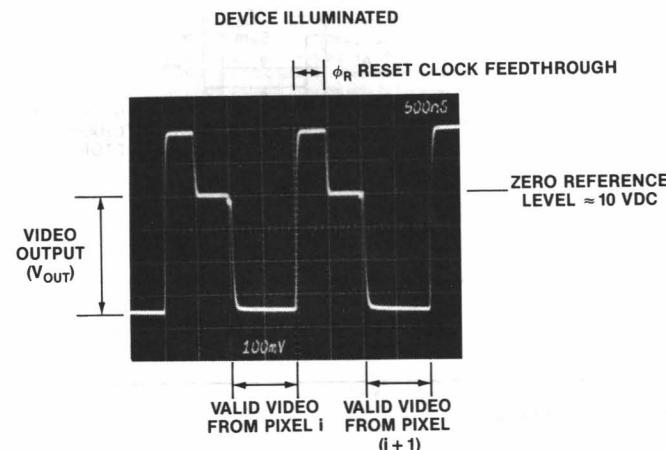

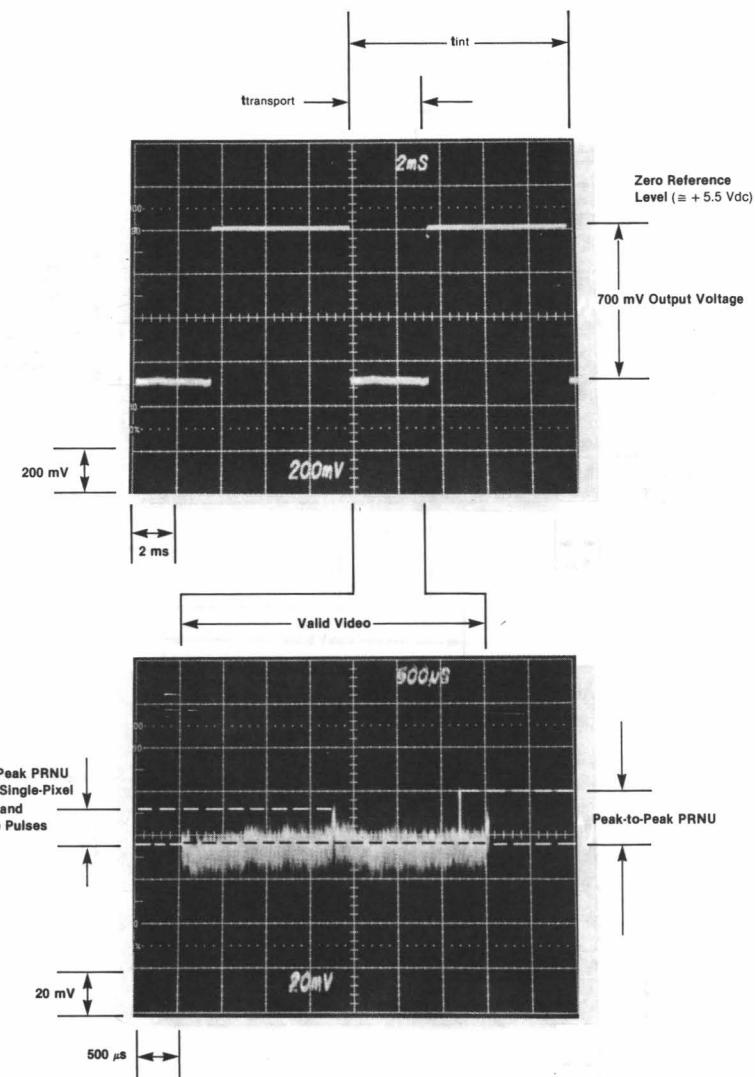

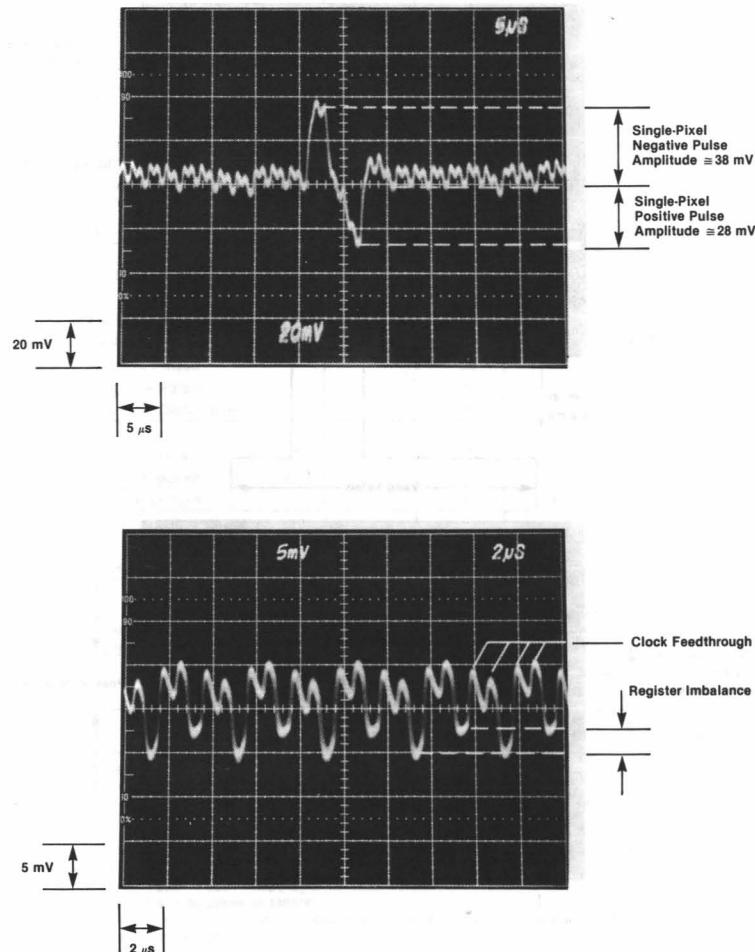

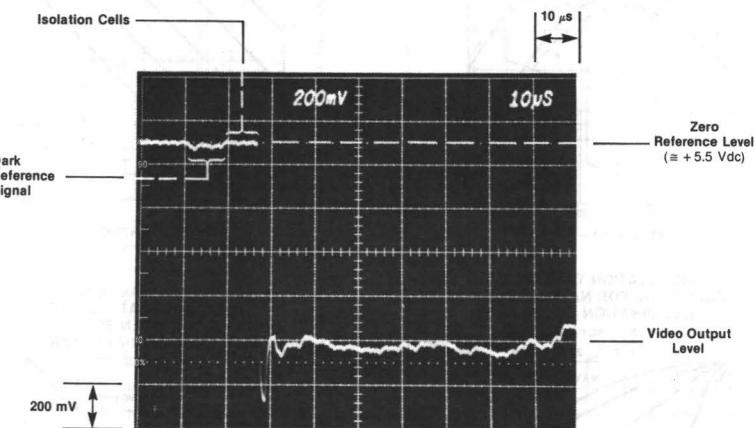

## Output with Uniform Illumination

TEST CONDITIONS:  $T_C = +25^\circ\text{C}$ ,  $t_{int} = 640 \mu\text{s}$ ,  $f_{\phi R} = 512 \text{ kHz}$ , "typ" voltage inputs, 2854°K + 700 nm cutoff filter set. (Half standard test speeds for clearer photos.)

**CCD111**

**Output of Two Pixels**

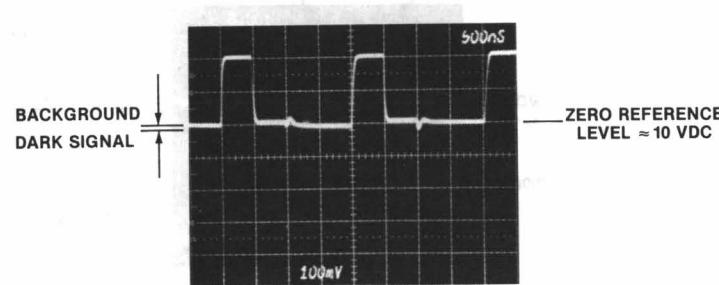

**DEVICE IN DARK**

**TEST CONDITIONS:**  $T_C = +25^\circ\text{C}$ ,  $t_{int} = 640 \mu\text{s}$ ,  $f_{\phi_R} = 512 \text{ kHz}$ , "typ" voltage inputs,  $2854^\circ\text{K} + 700 \text{ nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

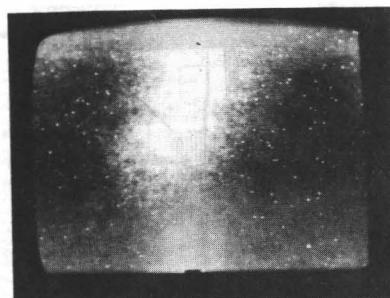

**CCD111**

**Photoresponse Non-uniformity**

MEASURED AT  $V_{out} = 350$  mV; ALL PRNU COMPONENTS EXCLUDE PIXELS #1 AND #256.

**TEST CONDITIONS:**  $T_C = +25^\circ\text{C}$ ,  $t_{int} = 320 \mu\text{s}$ ,  $f_{\phi_R} = 1.0 \text{ MHz}$ , "typ" voltage inputs,  $2854^\circ\text{K} + 700 \text{ nm}$  cutoff filter set.

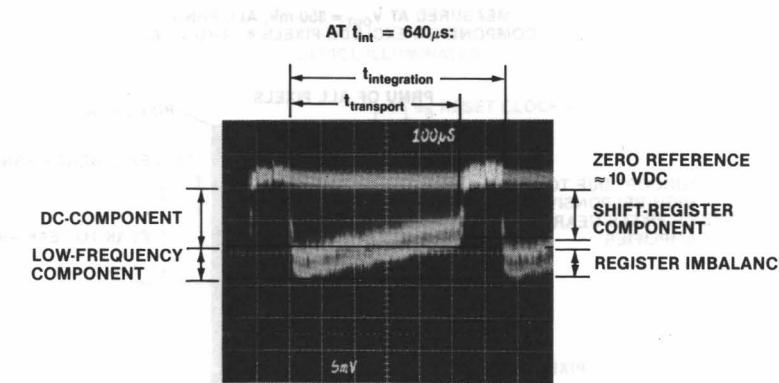

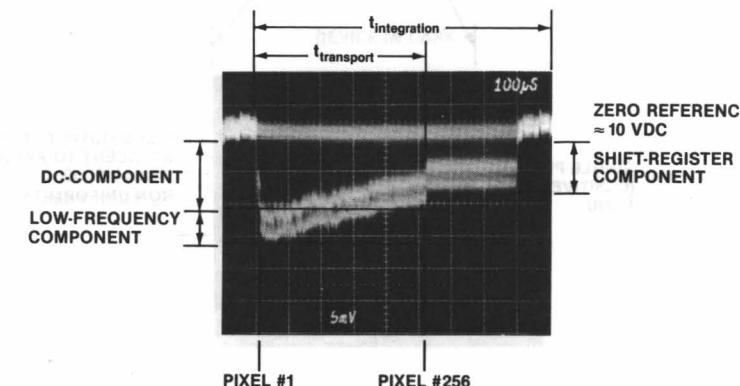

## CCD111

### DC + Low Frequency Dark Signal

AT  $t_{int} = 900\mu s$ , OTHER INPUTS SAME AS ABOVE:

TEST CONDITIONS:  $T_c = +25^\circ C$ ,  $t_{int} =$

(see above),  $f_{\phi R} = 512$  kHz, "typ" voltage

inputs. (Half standard test speeds for

clearer photos.)

## CCD111

### Single-pixel Dark Signal Non-uniformity

### Peripheral Response

## CCD111

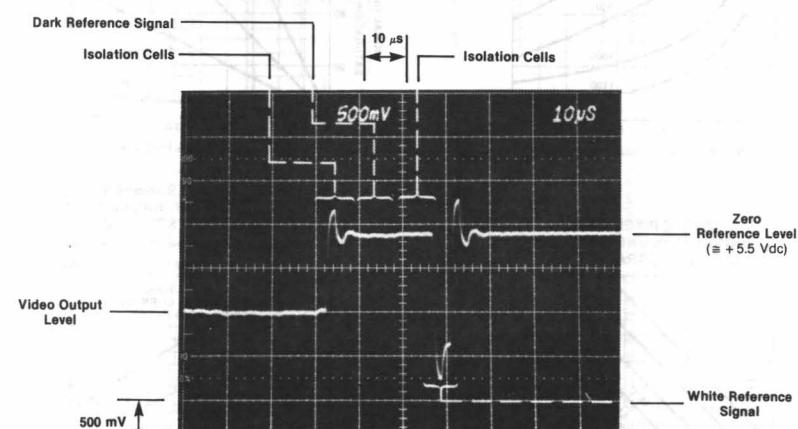

$\phi_X$ (Transfer Clock) Coupling into OS (Output)

## Device Care and Operation

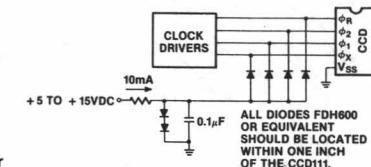

**Charge Injection:** Every input pin has a gate protection structure that includes a diode from the input to the (grounded) substrate  $V_{SS}$ . The diode is reverse-biased during normal operation ( $V_{in} > V_{SS}$ ). Negative (transient) input voltages ( $V_{in} < V_{SS}$ ) will forward-bias the diode, injecting electrons into the bulk silicon of the CCD chip.

If sufficient charge is injected, it will accumulate in the transport register(s) and/or the photosites near the injecting gate protection structure(s). Injected charge which accumulates in the photosites will typically result in an apparent bell-shaped increase in Dark Signal (= 20-200 pixels wide) near the injecting gate protection structure. Injected charge which accumulates in a transport register will result in an apparent uniform increase in that register's low frequency dark signal, creating a noticeable increase in the apparent Register Imbalance ("odd/even") of the Dark Signal.

The susceptibility to charge injection sufficient to increase the DC and Low Frequency Dark Signal varies significantly from device to device. It is not possible to select devices with "low" susceptibility. However, devices with low Dark Signal are typically more susceptible than devices with high Dark Signal.

Sufficient charge to appear as increased DC and Low Frequency Dark Signal may be injected by negative transient voltages  $< 4 \text{ ns}$  long. Since these transients

cannot be detected by oscilloscopes with less than 250-500 MHz bandwidth, a system which appears to be free from negative transients on a 200 MHz scope may still be prone to charge injection. The recommended method to eliminate charge injection is the following diode clipper circuit:

It is also important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The DC and Low Frequency Dark Signal approximately doubles for every  $5^\circ\text{C}$  temperature increase and Dark Signal Non-Uniformities approximately double for every  $8^\circ\text{C}$  increase. The devices may be cooled to achieve very long integration times and very low light level capability.

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with deionized water. Allow the glass to dry, preferably by blowing with filtered dry  $\text{N}_2$  or air.

## Typical Performance Curves

**CCD111**

**Typical Performance Curves (cont'd)**

NOTE:

DC and low-frequency dark signal temperature in bold and SPDSNU in parentheses.

**CCD111**

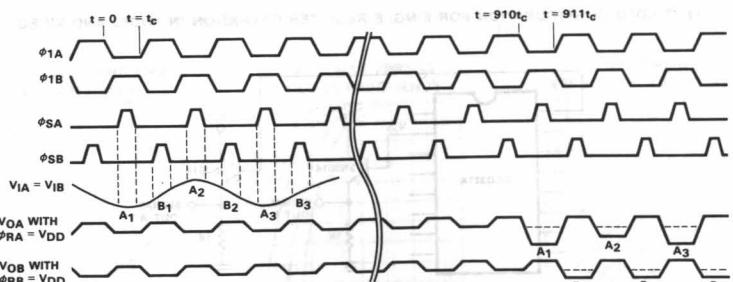

**Timing Diagram Drive Signals**

**Circuit Diagram**

17700

## CCD111

### Order Information

It is important to note that two different selections of the CCD111 are being offered for applications that differ in the wavelength of light used for imaging. Please refer to the section "Major Differences Between the CCD111A and CCD111B" on page 3 before placing an order.

To order the CCD111, please follow the ordering codes listed in the table below:

| Description                       | Device Type<br>Order Code |

|-----------------------------------|---------------------------|

| CCD111A 256 x 1 Line Image Sensor | CD111ADC                  |

| CCD111B 256 x 1 Line Image Sensor | CD111BDC                  |

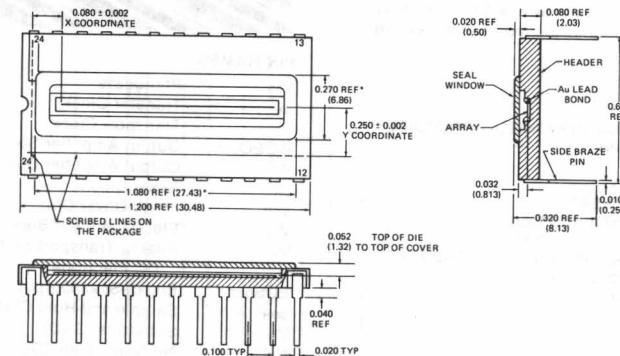

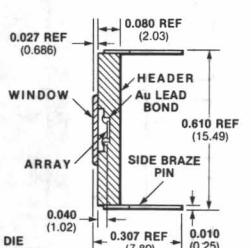

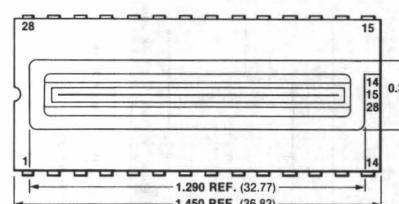

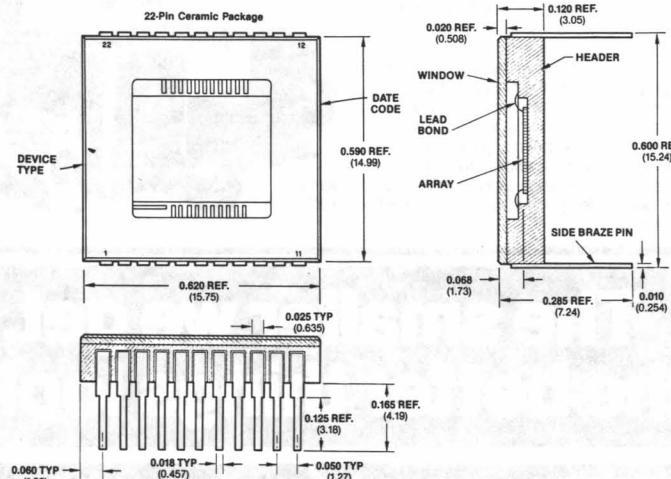

### CCD111DC Package Outline 18-Pin Dual In-Line Ceramic Package

#### NOTES:

All dimensions in inches (**bold**) and millimeters (parentheses). Header is black ceramic ( $\text{Al}_2\text{O}_3$ ). Glass window is attached to header with epoxy cement. Photosite #1 is located towards the notched end of the package. Terminal #9 is electronically connected to the Substrate ( $V_{SS}$ ).

## CCD121H

### 1728-ELEMENT LINEAR IMAGE SENSOR CHARGE COUPLED DEVICE

**GENERAL DESCRIPTION** — The CCD121H is a monolithic self-scanned 1728-Element Image Sensor designed for page scanning applications. The device provides a 200-line per inch resolution across an 8-1/2 inch page. Other intended applications are: facsimile readers, optical character recognition, as well as imaging applications that require high resolution, high sensitivity and high speed.

In addition to a row of 1728 sensing elements, the CCD121H chip includes: two charge transfer gates, two 2-phase analog shift registers, an output charge detector/preamplifier, and a compensation output amplifier. The 2-phase analog shift registers both feed the input of the charge detector resulting in sequential reading of the 1728 imaging elements.

The cell size is  $13\mu$  (0.51 mils) by  $17\mu$  (0.67 mils) on  $13\mu$  (0.51 mils) centers. The device is manufactured using Fairchild charge coupled device buried-channel technology.

- DYNAMIC RANGE TYPICAL: 500:1 (PEAK-TO-PEAK), 2500:1 (rms)

- 1728 ELEMENTS ON A SINGLE CHIP

- ON-CHIP PREAMPLIFIER AND COMPENSATION AMPLIFIER

- LOW POWER REQUIREMENTS

- ALL OPERATING VOLTAGES UNDER 15 V

- PACKAGED IN A 24-PIN DUAL IN-LINE HERMETIC PACKAGE

- LOW NOISE EQUIVALENT EXPOSURE

- WIDE RANGE OF VIDEO DATA RATE

- DIMENSIONALLY PRECISE PHOTOSITE SPACING

#### CONNECTION DIAGRAM DIP (TOP VIEW)

#### PIN NAMES

|                        |                                        |

|------------------------|----------------------------------------|

| PG                     | Photogate                              |

| $\phi_{XA}, \phi_{XB}$ | Transfer Gate Clocks                   |

| $\phi_{1A}, \phi_{2A}$ | Analog Shift Register Transport Clocks |

| $\phi_{1B}, \phi_{2B}$ |                                        |

| OG                     | Output Gate                            |

| OS                     | Output Transistor Source               |

| OD                     | Output Transistor Drain                |

| CS                     | Compensation Transistor Source         |

| $\phi_R$               | Reset Transistor Gate Clock            |

| RD                     | Reset Transistor Drain                 |

| TP                     | Test Point                             |

| $V_{SS}$               | Substrate (Ground)                     |

| NC                     | No Connection                          |

#### BLOCK DIAGRAM

## CCD121H

## ABSOLUTE MAXIMUM RATINGS (Above which useful life may be impaired)

Storage Temperature      -25°C to 100°C

Operating Temperature    -25°C to 55°C

Pins 3, 4, 7, 8, 9, 10, 13, 15, 16, 17, 18    -0.3 V to 12 V

Pins 2, 11, 14, 21, 22, 23                        -0.3 V to 18 V

**Caution Note:** The device has limited built-in gate protection. It is recommended to control and minimize static charge buildup. Care should be taken to avoid shorting leads OS and CS to ground during operation of the device.

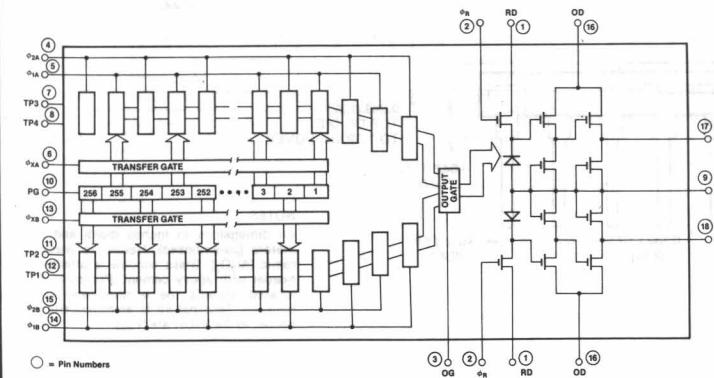

## FUNCTIONAL DESCRIPTION — The CCD121H consists of the following functional elements illustrated in the Block Diagram:

**Image Sensor Elements** — A row of 1728 Image Sensor Elements separated by diffused channel stops and covered by a silicon photogate. Image photons pass through the transparent polycrystalline silicon photogate and are absorbed in the single crystal silicon by hole-electron pair production. The photon generated electrons are accumulated in the photosites. The amount of signal charge accumulated is a linear function of the incident illumination intensity and the integration period. The output signal will vary in this analog manner from a thermally generated noise background at zero illumination to a maximum at saturation.

**Two Transfer Gates** — Gate structures adjacent to the row of Image Sensor Elements. The charge packets accumulated in the image sensor elements are transferred out via the transfer gates to the transport registers. Alternating charge packages are transferred to the left and right (A and B) analog transport shift registers. The HIGH states of the transfer-gates must be contained by the HIGH state of the transport shift register clocks. The next light integration period is started when transfer gates go LOW.

**Two 866-Bit Analog Shift Registers** — One on each side of the row of Image Sensor Elements and separated from it by a Transfer Gate. The two registers are used to move the image generated charge packets serially from the sensor elements to the Transfer Gate. The phase relationship of the last elements of the two shift registers provide for alternate charge detector/preamplifier. The phase relationship of the last elements of the two shift registers provide for alternate delivery of charge packets to re-establish the serial sequence of the photosites.

**A Gated Charge Detector/Preamplifier** — Charge packets are transported to a precharged diode whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of the output n-channel MOS transistor producing a signal output at OS. The reset transistor is driven by a reset clock ( $\phi_R$ ) so as to recharge the charge-detector diode capacitance before the arrival of each new signal charge packet from the transport registers.

## DEFINITION OF TERMS

**Charge Coupled Device** — A charge coupled device is a semiconductor device in which isolated charge-packets are transported from one position in the semiconductor to an adjacent position by sequential clocking by an array of gates. The charge-packets are minority carriers with respect to the semiconductor substrate.

**Transfer Gate Clock  $\phi_{XA}$ ,  $\phi_{XB}$**  — The voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD shift registers.

**Analog Shift Register Transport Clocks,  $\phi_{1A}$ ,  $\phi_{2A}$ ,  $\phi_{1B}$ ,  $\phi_{2B}$**  — The two sets of 2-phase clock applied to the gates of the CCD shift registers to move the charge packets received from the image sensor elements to the gated charge-detecting preamplifier.

**Gate Charge Detector Preamplifier** — The output circuit of the CCD121H which receives the charge packets from the CCD shift registers and provides a signal voltage proportional to the size of each charge packet. Before each new charge packet is sensed, a reset clock returns the output voltage to a base level.

**Reset Clock  $\phi_R$**  — The voltage waveform required to drive the gated charge detector preamplifier.

**Dynamic Range** — The saturation exposure divided by the peak-to-peak noise equivalent exposure.

This does not take into account dark signal non-uniformities or average dark signal. Dynamic range is sometimes defined in terms of rms noise. To compare the two definitions a factor of 4 to 6 is generally appropriate. (Peak-to-peak noise is approximately equal to 4 to 6 times rms noise.)

## CCD121H

## DEFINITION OF TERMS (Cont'd)

**Peak-to-Peak Noise Equivalent Exposure** — The exposure level which gives an output signal equal to the peak-to-peak noise level at the output in the dark.

**Saturation Exposure** — The minimum exposure level that will produce a saturated output signal. Saturation exposure is equal to the light intensity times the photosite integration time.

**Spectral Response Range** — The spectral band in which the response per unit of radiant power is more than 10% of the peak response.

**Responsivity** — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure level.

**Photoresponse Non-uniformity** — The difference of the response levels of the most and the least sensitive element under uniform illumination. This is commonly expressed as a percentage of the saturation output voltage.

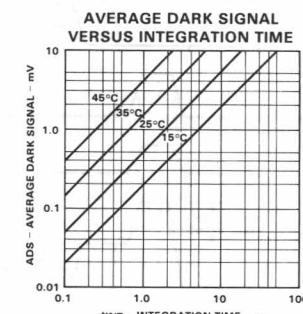

**Average Dark Signal** — The output signal level in the dark averaged over all elements and measured relative to the base line output voltage established by the reset clock. This is a linear function of the integration time. It is also strongly dependent on temperature. This is commonly expressed as a percentage of the saturation output voltage.

**Dark Signal Non-uniformity** — Maximum deviation of the output voltage of any element from the background level in the dark. This is commonly expressed as a percentage of the saturation output voltage.

**Saturation Output Voltage** — The maximum signal output voltage.

**Integration Time** — The time interval between the falling edges of any transfer pulse  $\phi_{XA}$  and  $\phi_{XB}$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

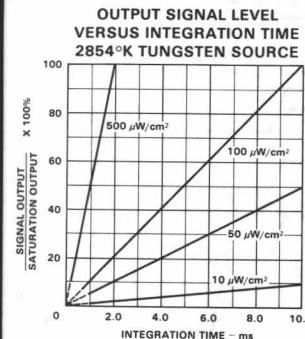

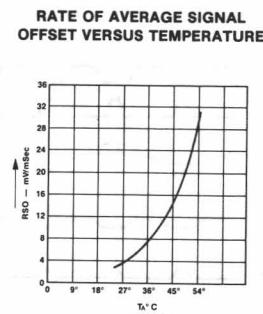

**Output Signal Range** — The output signal range is defined as  $OSR = V_{sat} \cdot (t_{INT} + t_{Transport}) \times \text{Rate of Average Signal Offset}$  where:  $t_{INT}$  = Integration Time;  $t_{Transport}$  = time necessary to transfer the charge packets from the analog shift registers and is equal to  $\frac{1728}{f_{\phi_R}}$ . Integration time ( $t_{INT}$ ) does not necessarily equal transfer time ( $t_{Transport}$ ). If long integration times are required,  $t_{Transport}$  should be minimized (increase  $f_{\phi_R}$ ) to maximize OSR.

**Average Signal Offset** — Average signal offset is a dc offset of the output voltage (due to the average leakage current in the CCD registers) which increases linearly with the transfer time.

## TEST LOAD CONFIGURATION

DC CHARACTERISTICS:  $T_A = 25^\circ C$

| SYMBOL   | CHARACTERISTIC                  | RANGE |      |      | UNITS | CONDITIONS          |

|----------|---------------------------------|-------|------|------|-------|---------------------|

|          |                                 | MIN   | TYP  | MAX  |       |                     |

| $V_{OD}$ | Output Transistor Drain Voltage | 14.5  | 15.0 | 15.5 | V     |                     |

| $V_{RD}$ | Reset Transistor Drain Voltage  | 11.5  | 12.0 | 12.5 | V     | Note 1              |

| $V_{OG}$ | Output Gate Voltage             | 4.5   | 5.0  | 5.5  | V     |                     |

| $V_{PG}$ | Photogate Voltage               | 10.0  | 10.3 | 10.5 | V     |                     |

| TP1, TP3 | Test Points                     |       | 0.0  |      | V     | Connect to $V_{SS}$ |

| TP2, TP4 | Test Points                     | 14.5  | 15.0 | 15.5 | V     |                     |

## CCD121H

CLOCK CHARACTERISTICS:  $T_A = 25^\circ\text{C}$

| SYMBOL                        | CHARACTERISTIC                                          | RANGE |      |     | UNITS | CONDITIONS |

|-------------------------------|---------------------------------------------------------|-------|------|-----|-------|------------|

|                               |                                                         | MIN   | TYP  | MAX |       |            |

| $V_{\phi1AL}$ - $V_{\phi1BL}$ | Analog Shift Register Transport Clocks LOW              | 0.0   | 0.5  | 0.8 | V     | Notes 2, 3 |

| $V_{\phi2AL}$ - $V_{\phi2BL}$ |                                                         |       |      |     |       |            |

| $V_{\phi1AH}$ - $V_{\phi1BH}$ | Analog Shift Register Transport Clocks HIGH             | 7.5   | 8.0  | 8.5 | V     | Notes 2, 3 |

| $V_{\phi2AH}$ - $V_{\phi2BH}$ |                                                         |       |      |     |       |            |

| $V_{\phi XAL}$                | Transfer Gate Clock LOW                                 | 0.0   | 0.5  | 0.8 | V     | Notes 2, 3 |

| $V_{\phi XAH}$                | Transfer Gate Clock HIGH                                | 7.5   | 8.0  | 8.5 | V     | Note 3     |

| $V_{\phi RL}$                 | Reset Clock LOW                                         | 0.0   | 0.5  | 0.8 | V     | Notes 2, 3 |

| $V_{\phi RH}$                 | Reset Clock HIGH                                        | 7.5   | 8.0  | 8.5 | V     | Note 3     |

| $f_{\phi1A}$ - $f_{\phi1B}$   | Maximum Analog Shift Register Transport Clock Frequency |       | 5.0  |     | MHz   | Notes 4, 5 |

| $f_{\phi2A}$ - $f_{\phi2B}$   |                                                         |       |      |     |       |            |

| $f_{\phi R}$                  | Maximum Reset Clock Frequency (Output Bit Rate)         |       | 10.0 |     | MHz   | Notes 4, 5 |

AC CHARACTERISTICS:  $T_A = 25^\circ\text{C}$ ,  $f_{\phi1} = f_{\phi2} = 0.5 \text{ MHz}$ ,  $f_{\phi R} = 1 \text{ MHz}$ ,  $t_{\text{INT}} \cong 1.78 \text{ ms}$ ,  $t_{\text{TRANSPORT}} = 1.73 \text{ ms}$ , See Note 14.

| SYMBOL           | CHARACTERISTIC                         | RANGE |                    |          | UNITS                           | CONDITIONS                     |

|------------------|----------------------------------------|-------|--------------------|----------|---------------------------------|--------------------------------|

|                  |                                        | MIN   | TYP                | MAX      |                                 |                                |

| DR               | Dynamic Range                          | 250   | 500                |          |                                 | Notes 6, 7                     |

| NEE              | Peak-to-Peak Noise Equivalent Exposure |       | $1 \times 10^{-3}$ |          | $\mu\text{j}/\text{cm}^2$       | Note 7                         |

| SE               | Saturation Exposure                    |       | 1.0                |          | $\mu\text{j}/\text{cm}^2$       | Note 7                         |

| SR               | Spectral Response Range Limits         |       | 0.45-1.05          |          | $\mu\text{m}$                   |                                |

| R                | Responsivity                           |       | 0.5                |          | V per $\mu\text{j}/\text{cm}^2$ | Notes 9, 10, 11                |

| PRNU             | Photoresponse Non-uniformity           |       | $\pm 25$           | $\pm 50$ | mV                              | Note 8                         |

| ADS              | Average Dark Signal                    |       | 5.0                | 25       | mV                              | Note 12                        |

| DSNU             | Dark Signal Non-uniformity             |       | 20                 | 50       | mV                              | Note 13                        |

| $V_{\text{sat}}$ | Saturation Output Voltage              | 500   | 750                | 1000     | mV                              | Notes 9, 10                    |

| $V_O$            | Output DC Level                        |       | 7.5                |          | V                               |                                |

| P                | Power Dissipation                      |       | 165                |          | mW                              | $V_{\text{OD}} = 15 \text{ V}$ |

| Z                | Output Impedance                       |       | 1000               |          | $\Omega$                        |                                |

| N                | Peak-to-Peak Noise                     |       | 1.0                |          | mV                              |                                |

| RSO              | Rate of Average Signal Offset          |       | 2.5                |          | mV/ms                           |                                |

NOTES:

1.  $V_{\phi RH}$  should track  $V_{RD}$ .

2. Negative transients on the clocks below 0.0 V may cause an increase in apparent dark signal.

3.  $C_{\phi XA} = C_{\phi XB} = C_{\phi 1A} = C_{\phi 1B} = C_{\phi 2A} = C_{\phi 2B} \cong 400 \text{ pF}$ ,  $C_{\phi RA} = C_{\phi RB} \cong 10 \text{ pF}$ .

4. The resulting data output frequency is twice that of each analog shift register clock,  $f_{\phi1A}$ ,  $f_{\phi2A}$ ,  $f_{\phi1B}$ ,  $f_{\phi2B}$ .

5. Minimum clock frequency is limited by increase in dark current which reduces output signal range OSR. See curves.

6. The dynamic range is measured by taking the ratio of the saturation output voltage to the peak-to-peak noise of the device in the dark. Because of the high degree of linearity of the device the dynamic range measurement is also approximately equal to the ratio of the saturation exposure to the peak-to-peak noise equivalent exposure.

7.  $1 \mu\text{j}/\text{cm}^2 = 0.02 \text{ fcs}$  at  $2854^\circ\text{K}$ ,  $1 \text{ fcs} = 50 \mu\text{j}/\text{cm}^2$  at  $2854^\circ\text{K}$ .

8. Measurement is done at  $\approx 350 \text{ mV}$  output level. Measurement excludes first and last elements but includes both registers' outputs.

9. See test load configurations.

10. See definition of terms.

11. For  $2854^\circ\text{K}$  light source.

12. See curve.

13. DSNU has similar integration time and temperature dependence as ADS.

14. It is recommended to use an infrared blocking filter to obtain minimum PRNU and crosstalk.

## CCD121H

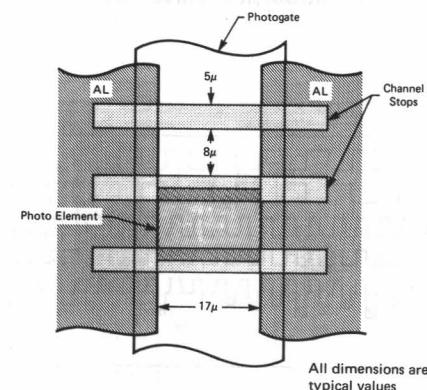

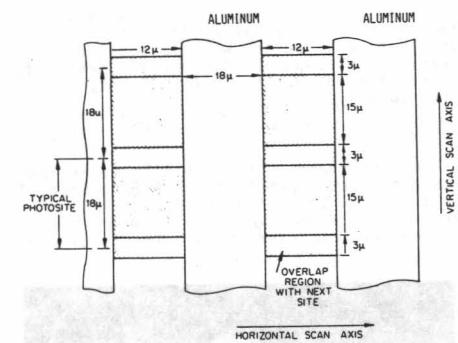

### PHOTOELEMENT DIMENSIONS

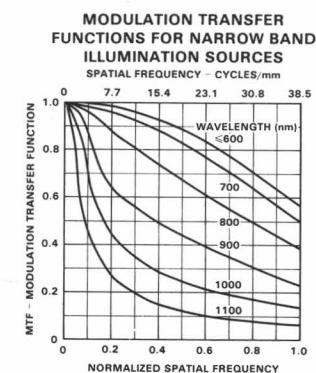

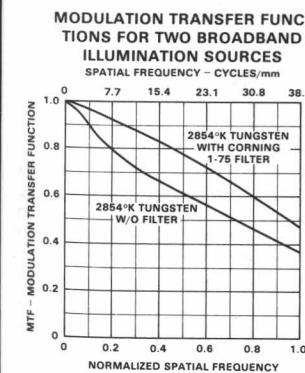

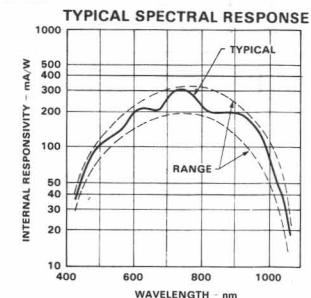

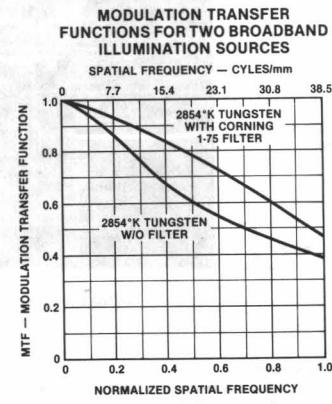

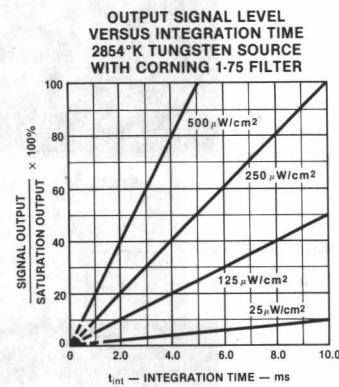

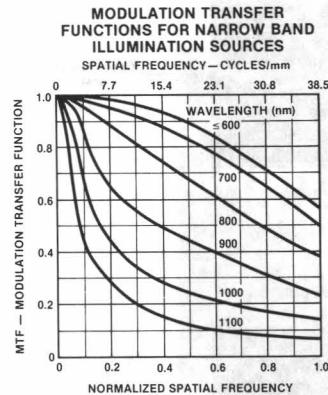

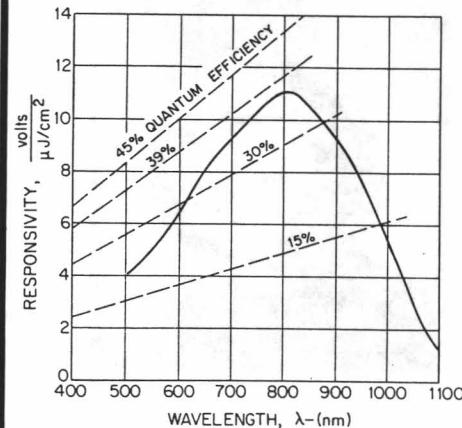

### TYPICAL PERFORMANCE CURVES

The Corning 1-75 filter has the following typical transmittance spectral characteristic:

$>85\%$  at  $<600 \text{ nm}$ ,  $60\%$  at  $700 \text{ nm}$ ,  $30\%$  at  $800 \text{ nm}$ ,  $5\%$  at  $900 \text{ nm}$  and  $<2\%$  at  $>1000 \text{ nm}$ .

CCD121H

CCD121H

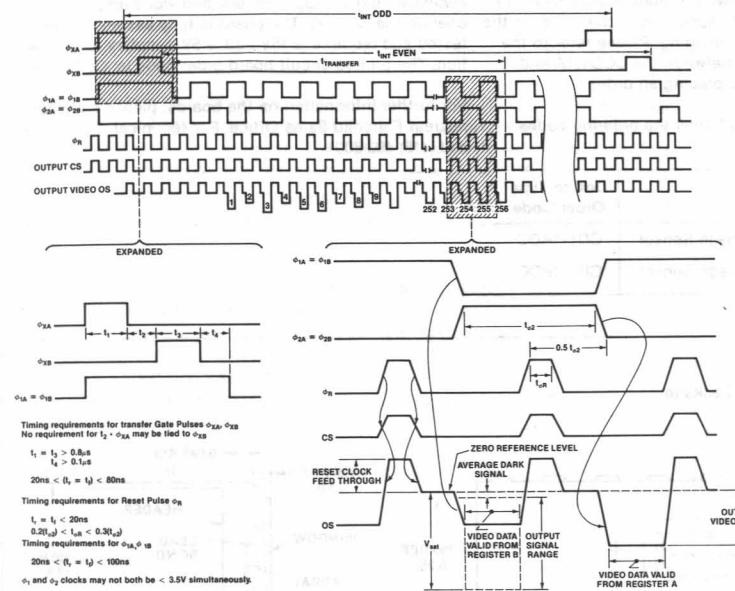

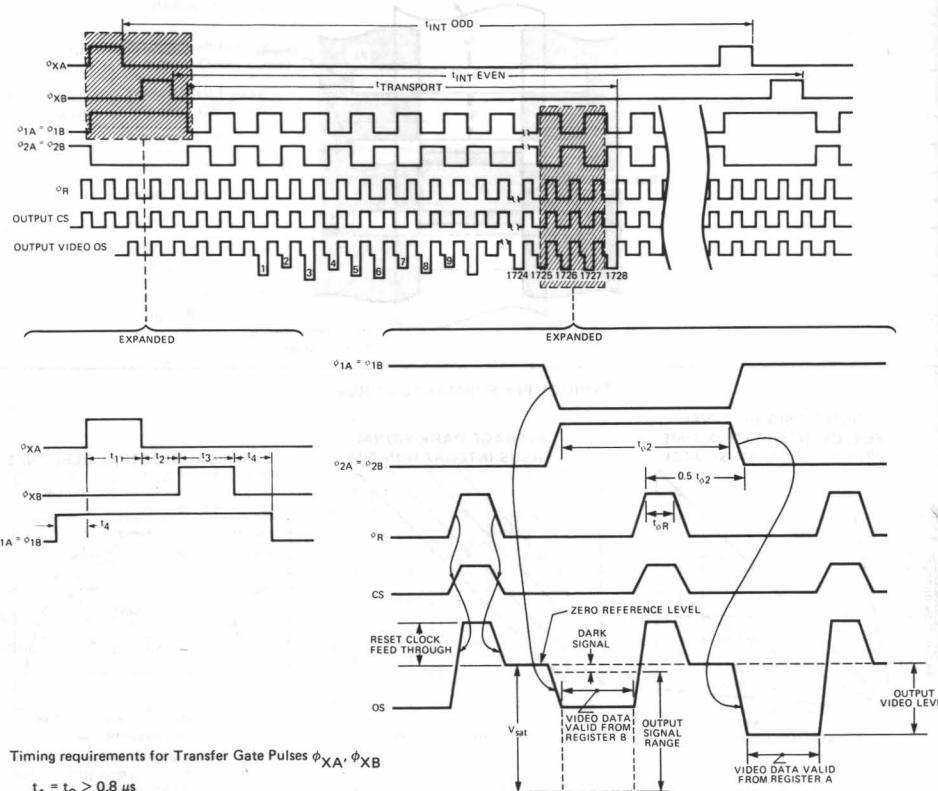

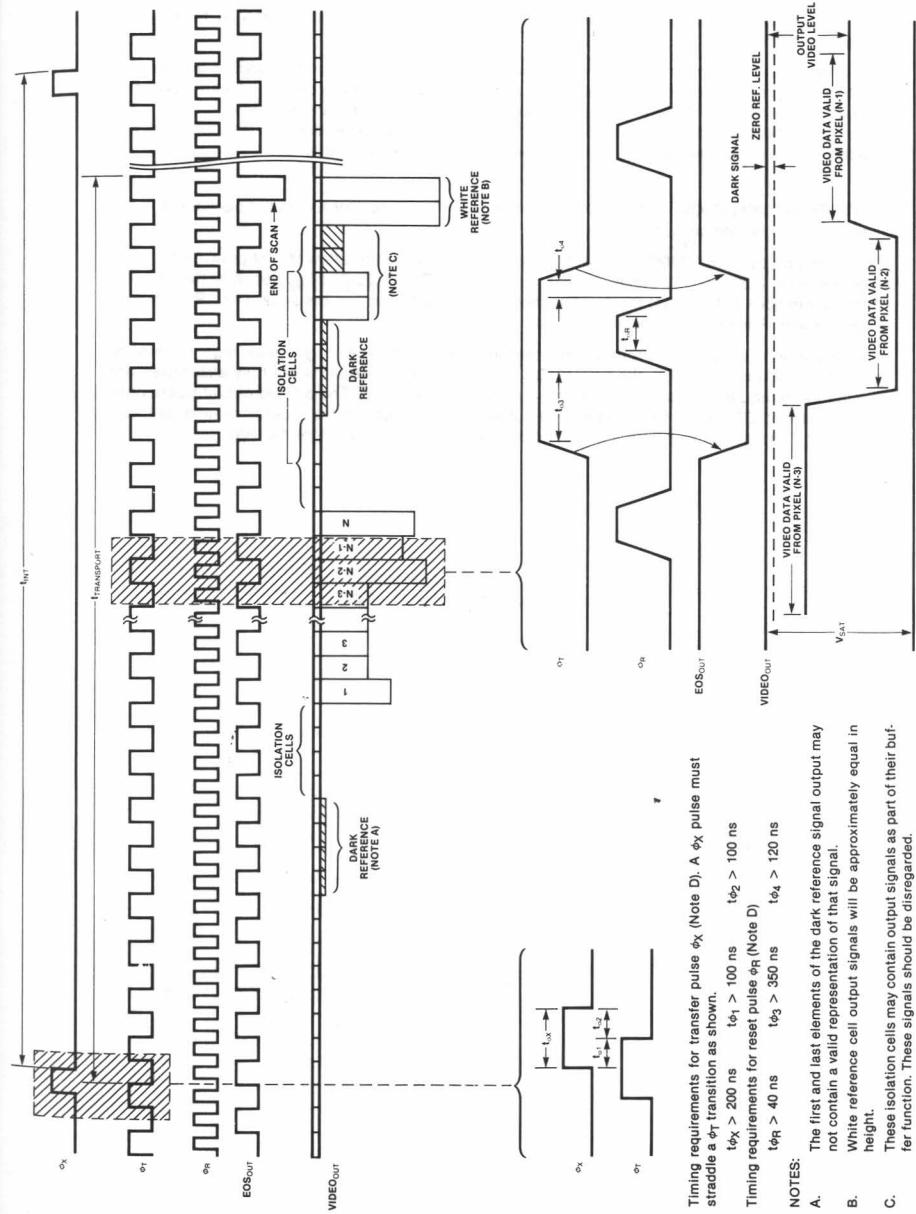

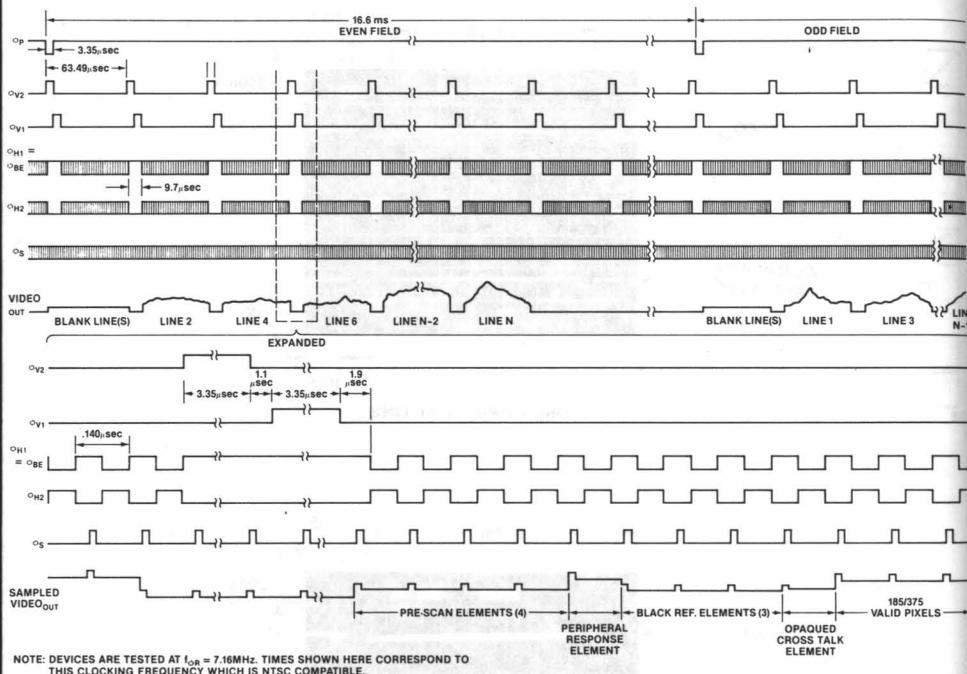

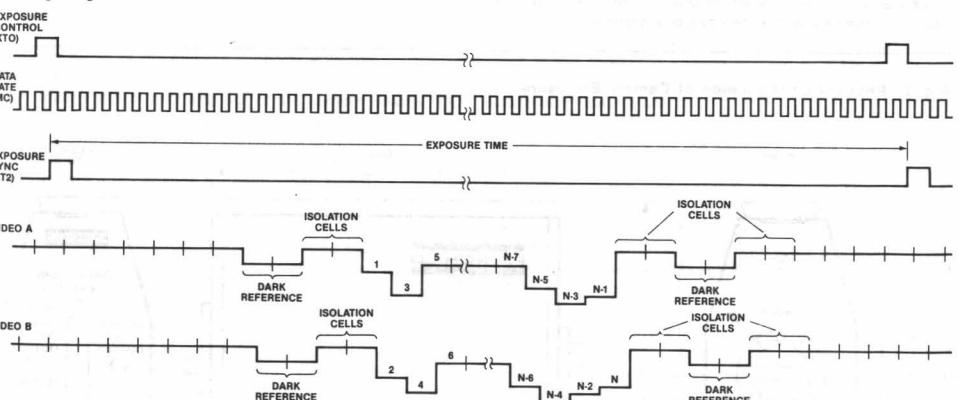

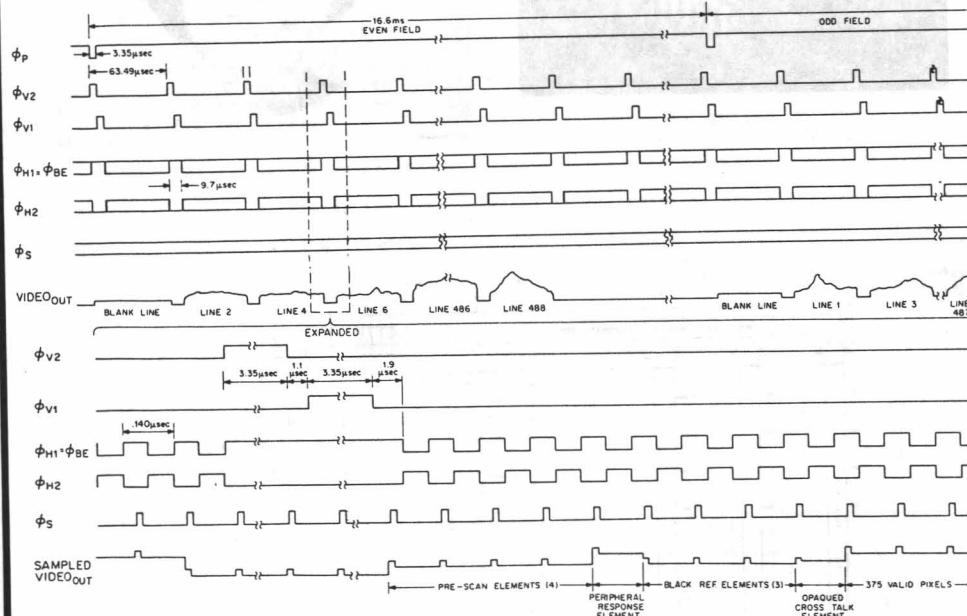

### TIMING DIAGRAM DRIVE SIGNALS

Timing requirements for Transfer Gate Pulses  $\phi_{XA}, \phi_{XB}$

$$t_1 = t_3 > 0.8\ \mu s$$

$$t_2 = t_4 > 0.1\ \mu s$$

Timing requirements for Reset Pulse  $\phi_R$

$$t_r = t_f < 0.3\ (\phi_R)$$

$$0.25\ (\phi_2) < t\phi_R < 0.5\ (\phi_2)$$

Timing requirements for  $\phi_{1A} = \phi_{1B}$

$$0.1\ (\phi_2) < (t_r = t_f) < 0.4\ (\phi_2)$$

CCD121H

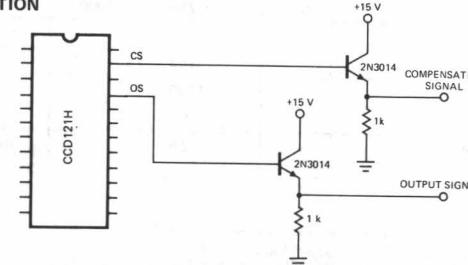

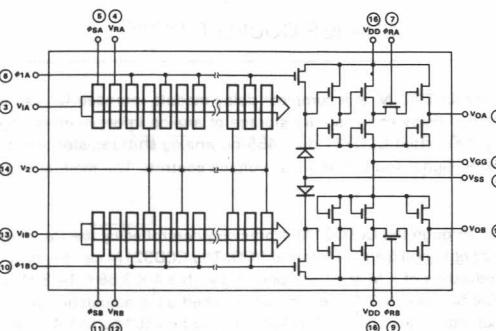

### CIRCUIT DIAGRAM

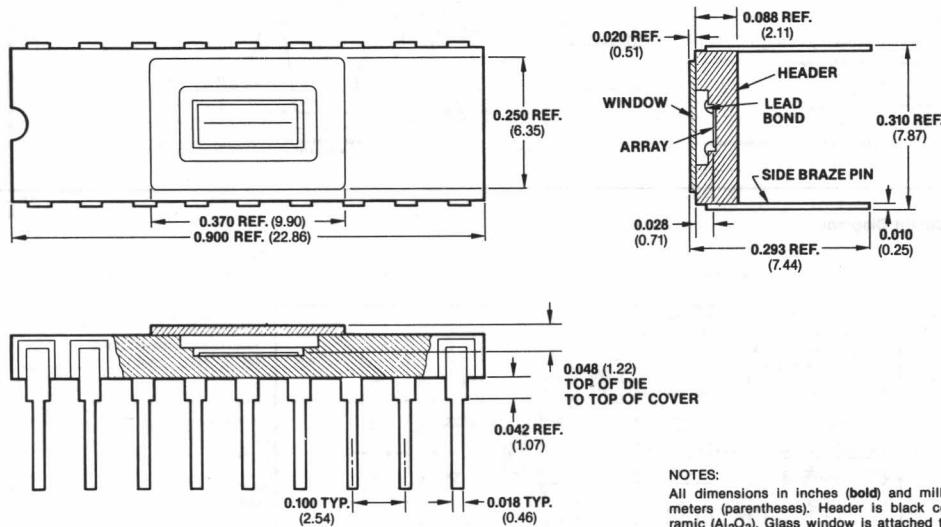

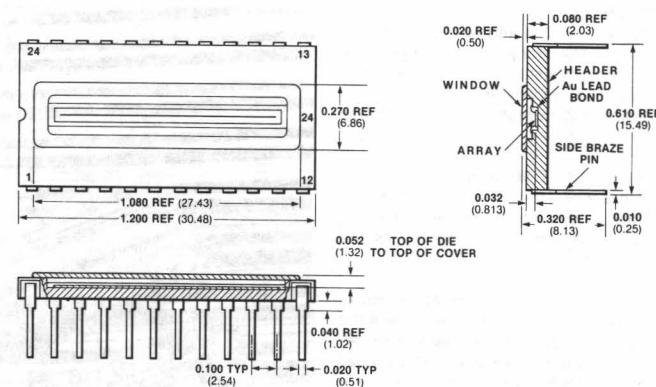

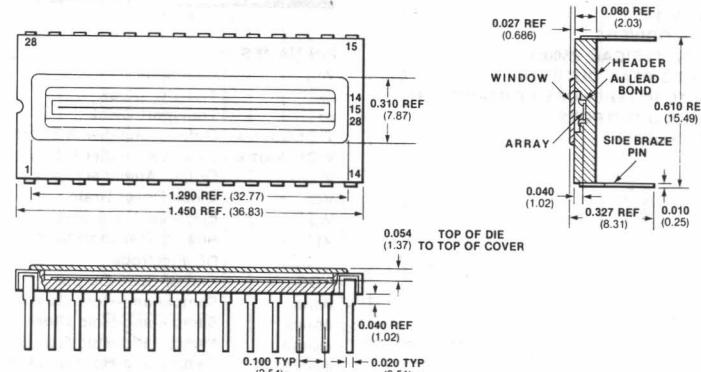

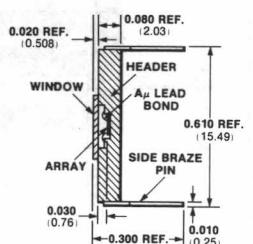

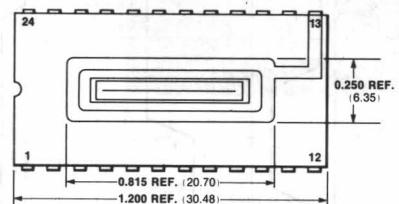

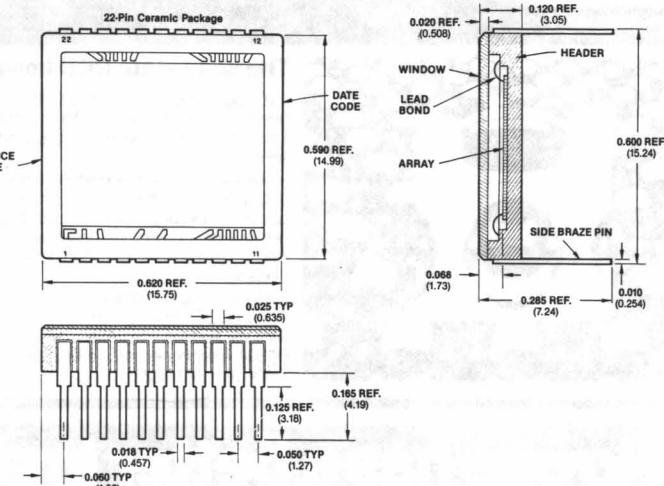

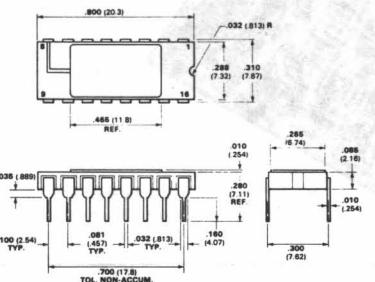

### PACKAGE OUTLINE 24-Pin Dual In-line Hermetic Package

### NOTES:

All dimensions in inches (bold) and millimeters (parenthesis). Header is black ceramic ( $Al_2O_3$ ). Transparent portion of package is glass. The CCD121H hermetic package carries the number "24" close to pin 1 of the device. This number should not be confused with pin 24 of the device is connected to  $V_{SS}$  (substrate).

**ORDER INFORMATION** — Order CCD121HC where "H" stands for hermetic package and "C" is commercial temperature range. The CCD121HC is the replacement for the CCD121DC. The two devices are pin-for-pin compatible. The output on-chip amplifier of the CCD121H is an improved design (over the CCD121) providing a higher saturation output voltage of typically 750 mV.

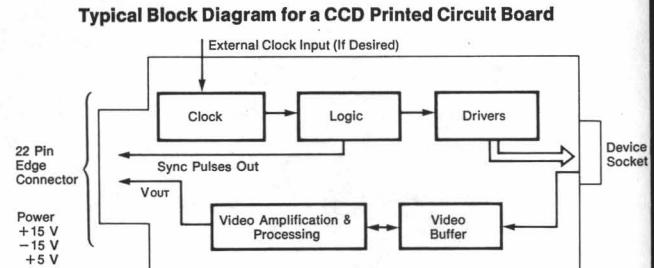

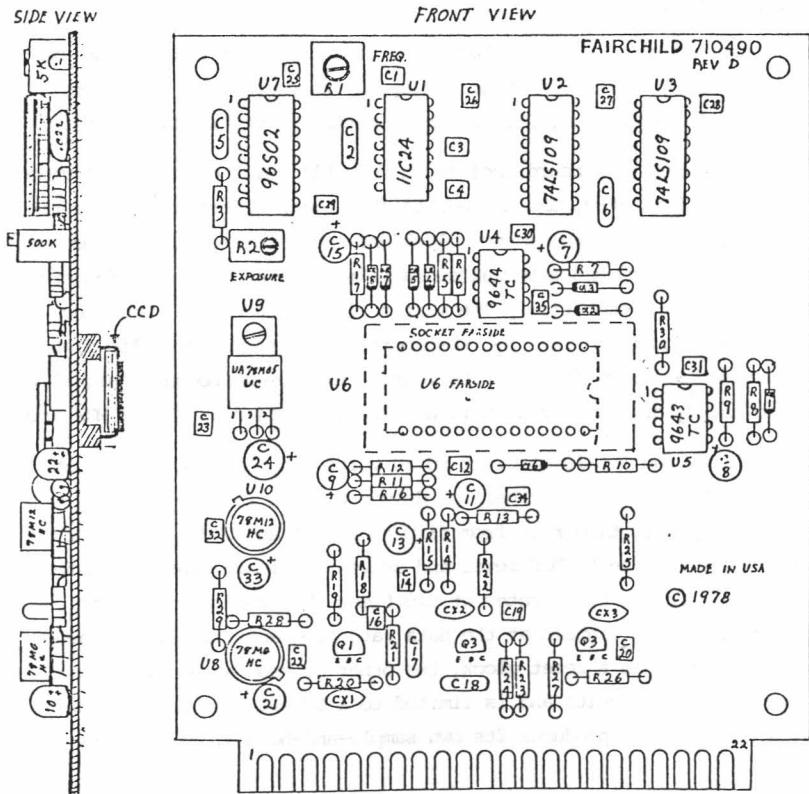

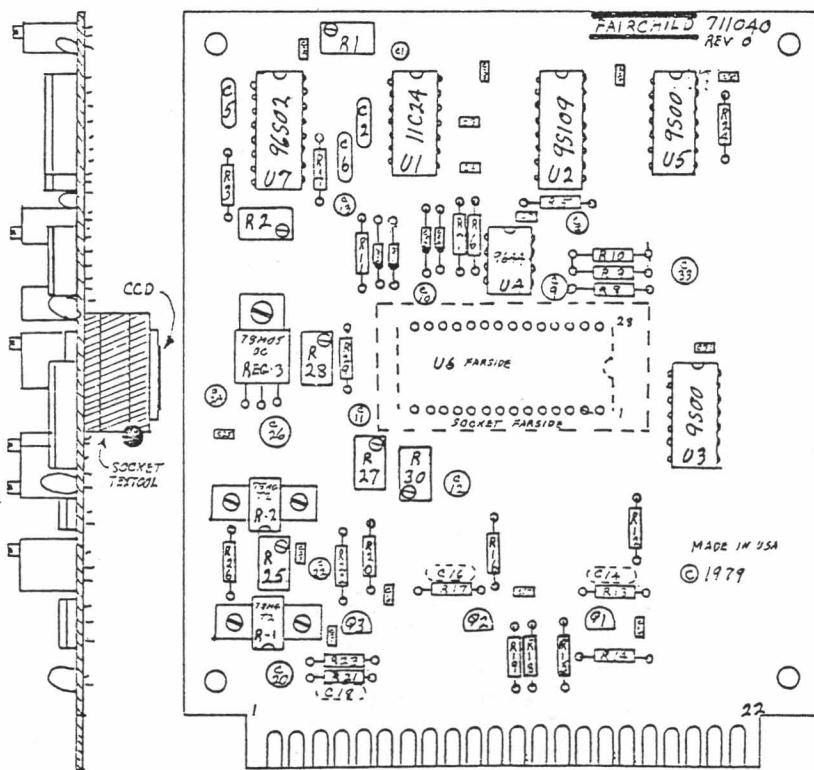

Also available is a printed circuit board that includes all the necessary clocks, logic, drivers and video amplifiers to operate the CCD121H. The printed circuit board is fully assembled and tested and requires three power supplies for operation (+5 V, +15 V and -15 V). The printed circuit board order code is: CCD121HB.

HISTOGRAM

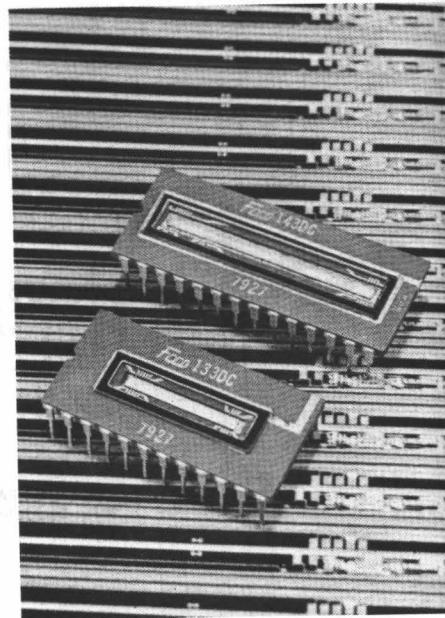

**CCD122/142**

1728/2048-ELEMENT LINEAR IMAGE SENSOR

FAIRCHILD CHARGE COUPLED DEVICE

**GENERAL DESCRIPTION**—The CCD122 and CCD142 are monolithic 1728 and 2048-element line image sensors, respectively. The devices are designed for page scanning applications including facsimile, optical character recognition and other imaging applications which require high resolution and high sensitivity.

The 1728 sensing elements of the CCD122 provide a 200-line per inch resolution across an 8-1/2 inch page adopted as an international facsimile standard. The 2048 sensing elements of the CCD142 provide an 8-line per millimeter resolution across a 256 millimeter page adopted as the Japanese facsimile standard.

The CCD122 and the CCD142 have overall improved performance compared with the CCD121H including higher sensitivity, an enhanced blue response and a lower dark signal. The devices also incorporate on-chip clock driver circuitry.

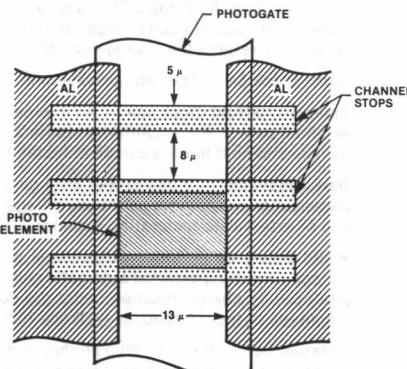

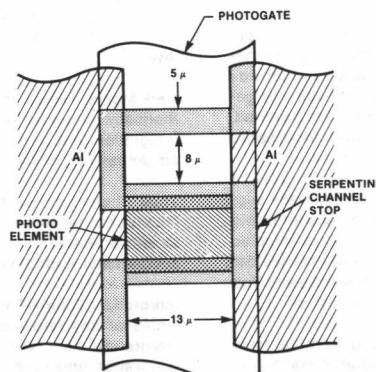

The photoelement size is  $13 \mu$  (0.51 mils) by  $13 \mu$  (0.51 mils) on  $13 \mu$  (0.51 mils) centers. The devices are manufactured using Fairchild advanced charge-coupled device n-channel Isoplanar buried-channel technology.

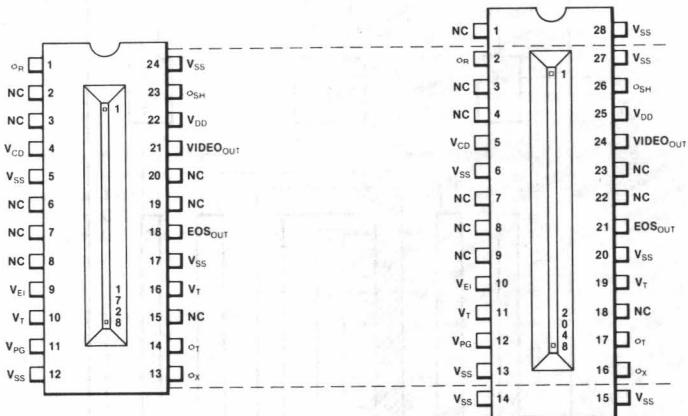

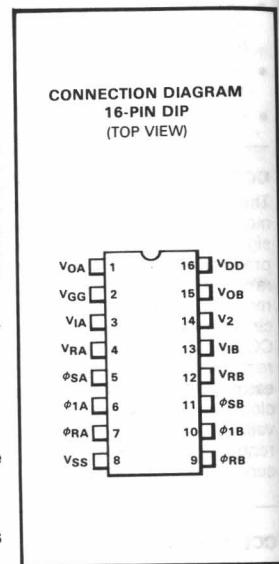

**PIN NAMES**

|                    |                                                 |

|--------------------|-------------------------------------------------|

| V <sub>PG</sub>    | Photogate                                       |

| $\phi_x$           | Transfer Clock                                  |

| $\phi_t$           | Transport Clock                                 |

| V <sub>DD</sub>    | Output Amplifier Source                         |

| V <sub>DD</sub>    | Output Amplifier Drain                          |

| $\phi_R$           | Reset Clock                                     |

| V <sub>CD</sub>    | Clock Driver Drain                              |

| V <sub>EI</sub>    | Electrical Input Bias                           |

| V <sub>T</sub>     | Analog Transport Shift Register<br>DC Electrode |

| EOS <sub>OUT</sub> | End-of-Scan Output                              |

| $\phi_{SH}$        | Sample-and-Hold Clock                           |

| V <sub>SS</sub>    | Substrate (GND)                                 |

| NC                 | No Connection (Do not Ground)                   |

533-90

**CCD122/142 VS. CCD121H COMPARISON**

| PARAMETER                           | CCD122/142      | CCD121H |

|-------------------------------------|-----------------|---------|

| Spectral Response — Blue<br>Overall | 4:1 Improvement | —       |

| Dark Signal<br>Responsivity         | 2:1 Improvement | —       |

| On-Chip Clock Drivers               | 2:1 Improvement | —       |

| Dark and White References           | Yes             | No      |

| Single Power Supply                 | Yes             | No      |

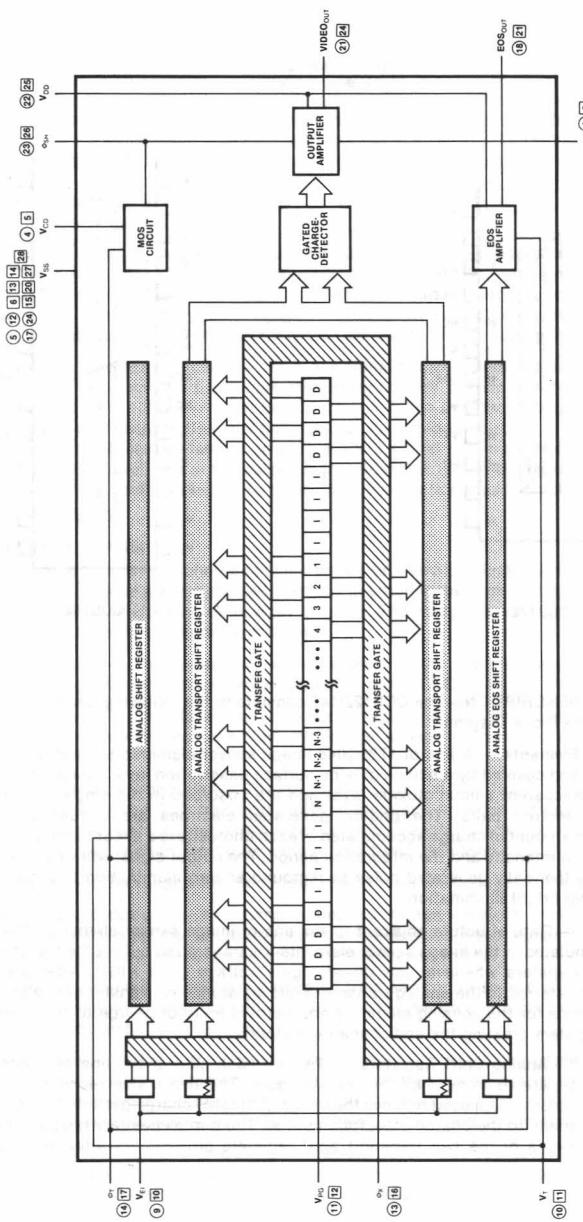

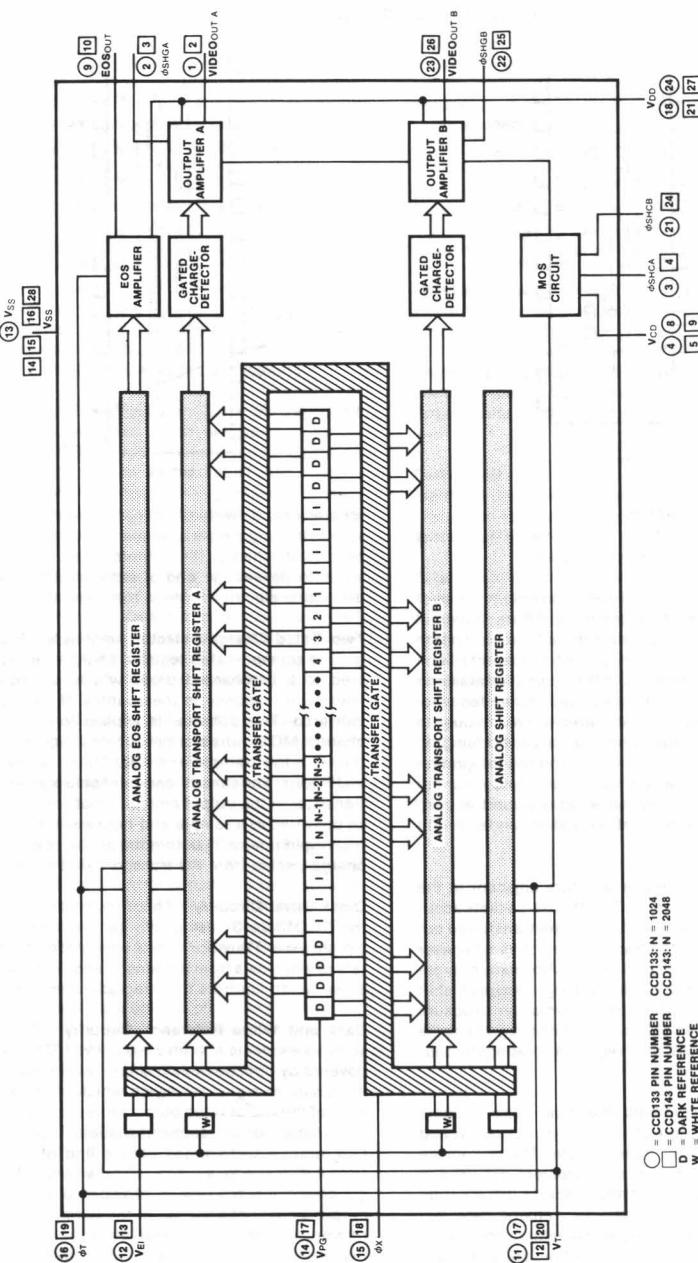

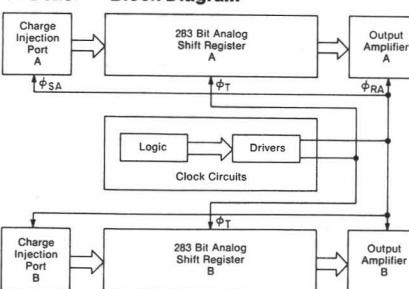

BLOCK DIAGRAM

**CCD122/142**

○ = CCD122 Pin Number

□ = CCD142 Pin Number

D = Dark Reference

W = White Reference

- = Isolation Cell

CCD122: N = 1728

CCD142: N = 2048

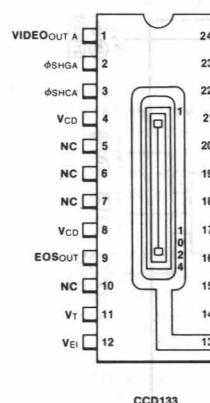

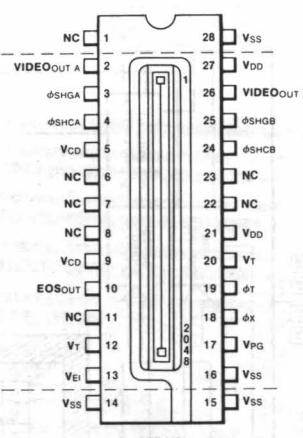

CONNECTION DIAGRAM

DIP (TOP VIEW)

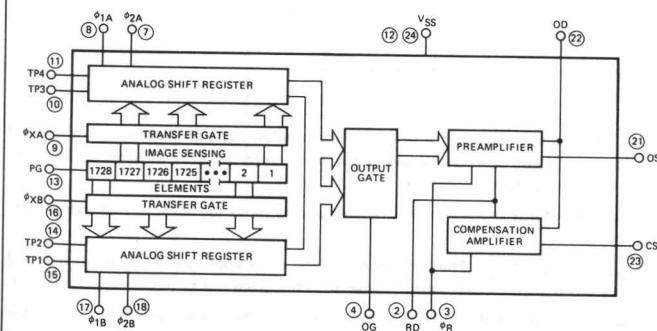

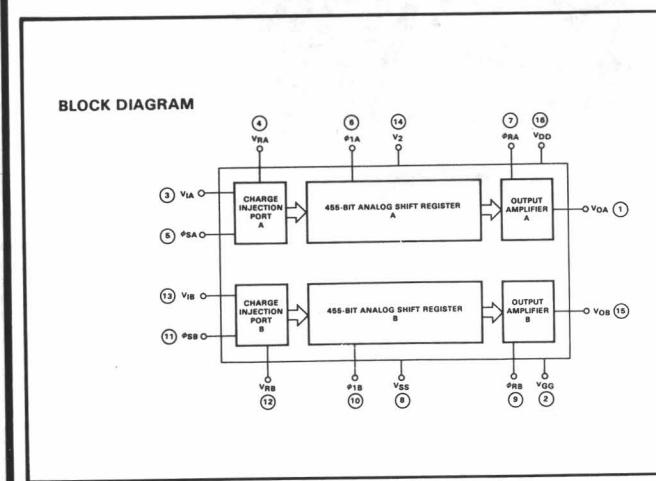

**FUNCTIONAL DESCRIPTION**—The CCD122/142 consists of the following functional elements illustrated in the Block Diagram:

**Image Sensor Elements** — A line of 1728/2048 image sensor elements separated by diffused channel stops and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon dioxide layer and are absorbed in the single crystal silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated noise background at zero illumination to a maximum at saturation under bright illumination.

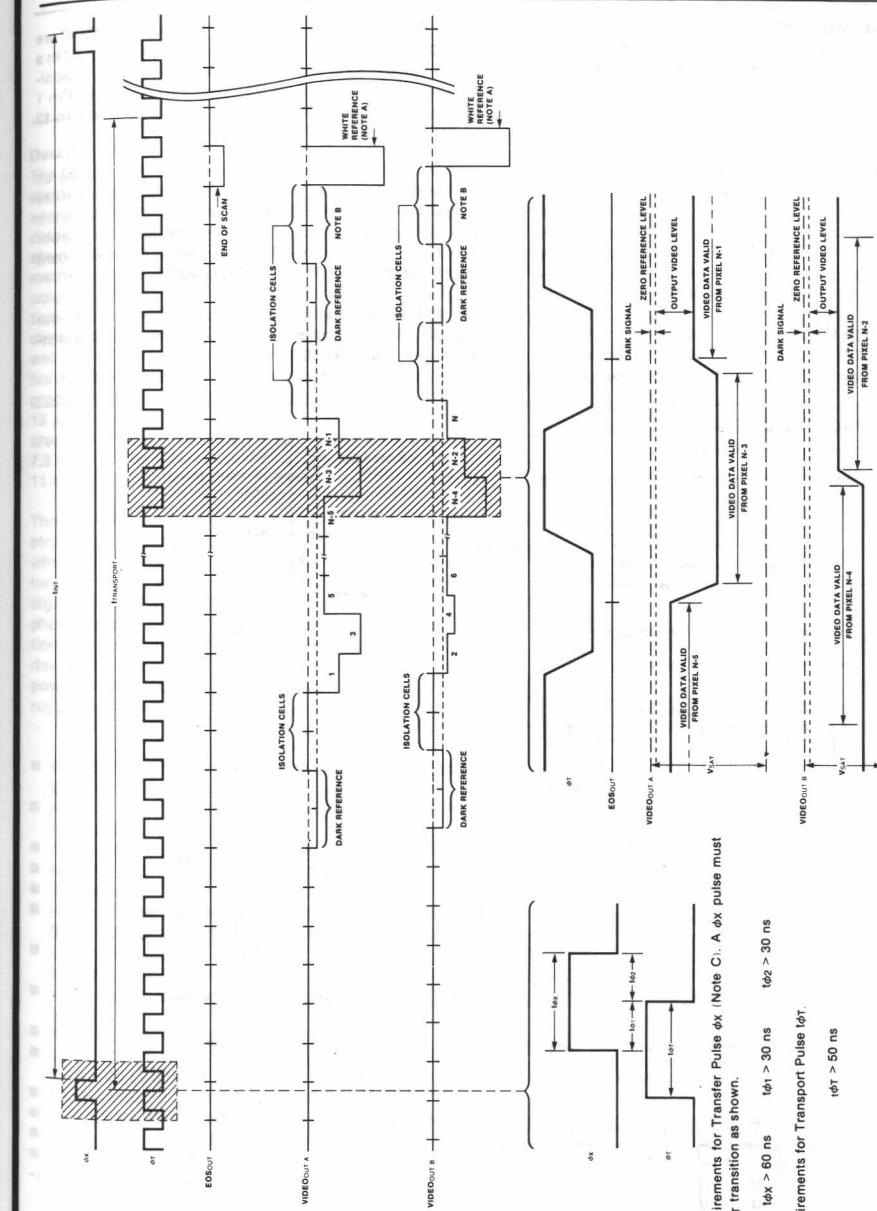

**Transfer Gate** — Gate structure adjacent to the line of image sensor elements. The charge-packets accumulated in the image sensor elements are transferred out via the transfer gate to the transport registers whenever the transfer gate voltage goes HIGH. Alternate charge-packets are transferred to the analog transport shift registers. The transfer gate also controls the exposure time for the sensing elements and permits entry of charge to the End-Of-Scan (EOS) shift registers creating the end-of-scan waveform.

**Four 879/1039-Bit Analog Shift Registers** — Two on each side of the line of image sensor elements and separated from it by the transfer gate. The two inside registers, called the transport shift registers, are used to move the image generated charge-packets delivered by the transfer gate serially to the charge-detector/amplifier. The complementary phase relationship of the last elements of the two transport shift registers provides for alternate delivery of

charge-packets to establish the original serial sequence of the line of video in the output circuit. The outer two registers serve to deliver the end-of-scan waveform and reduce peripheral electron noise in the inner shift registers.

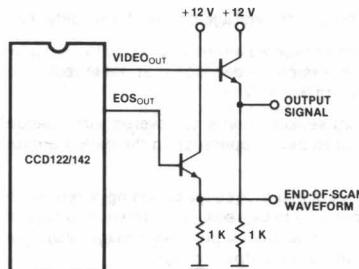

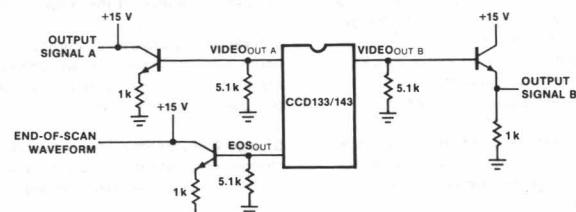

**Gated Charge-Detector/Amplifier** — Charge-packets are transported to a precharged diode whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of an n-channel MOS transistor producing a signal which passes through the sample-and-hold gate to the output at VIDEO<sub>OUT</sub>. The sample-and-hold gate is a switching MOS transistor in the output amplifier that allows the output to be delivered as a sampled-and-held waveform. A reset transistor is driven by the Reset Clock ( $\phi_R$ ) and recharges the charge-detector diode capacitance before the arrival of each new signal charge-packet from the transport registers.

**Clock Driver Circuitry** — Allows the CCD122/142 to be operated using only three external clocks, (1) a Reset Clock signal which controls the integrated output signal amplifier, (2) a square wave Transport Clock which operates at half the reset clock frequency and controls the readout rate of video data from the sensor, and (3) a Transfer Clock pulse which controls exposure time of the sensor. The external clocks should be able to supply TTL level power.

**Dark and White Reference Circuitry** — Four additional sensing elements at both ends of the 1728/2048 array are covered by opaque metalization. They provide a dark (no illumination) signal reference which is delivered at both ends of the line of video output representing the illuminated 1728/2048 sensor elements (labelled "D" in the block diagram). Also included at one end of the 1728/2048 sense element array is a white signal reference level generator which likewise provides a reference in the output signal (labelled "W" in the block diagram). These reference levels are useful as inputs to external DC restoration and/or automatic gain control circuitry.

#### DEFINITION OF TERMS:

**Charge-Coupled Device** — A charge-coupled device is a semiconductor device in which finite isolated charge-packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge-packets are minority carriers with respect to the semiconductor substrate.

**Transfer Clock  $\phi_x$**  — The voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD transport shift registers.

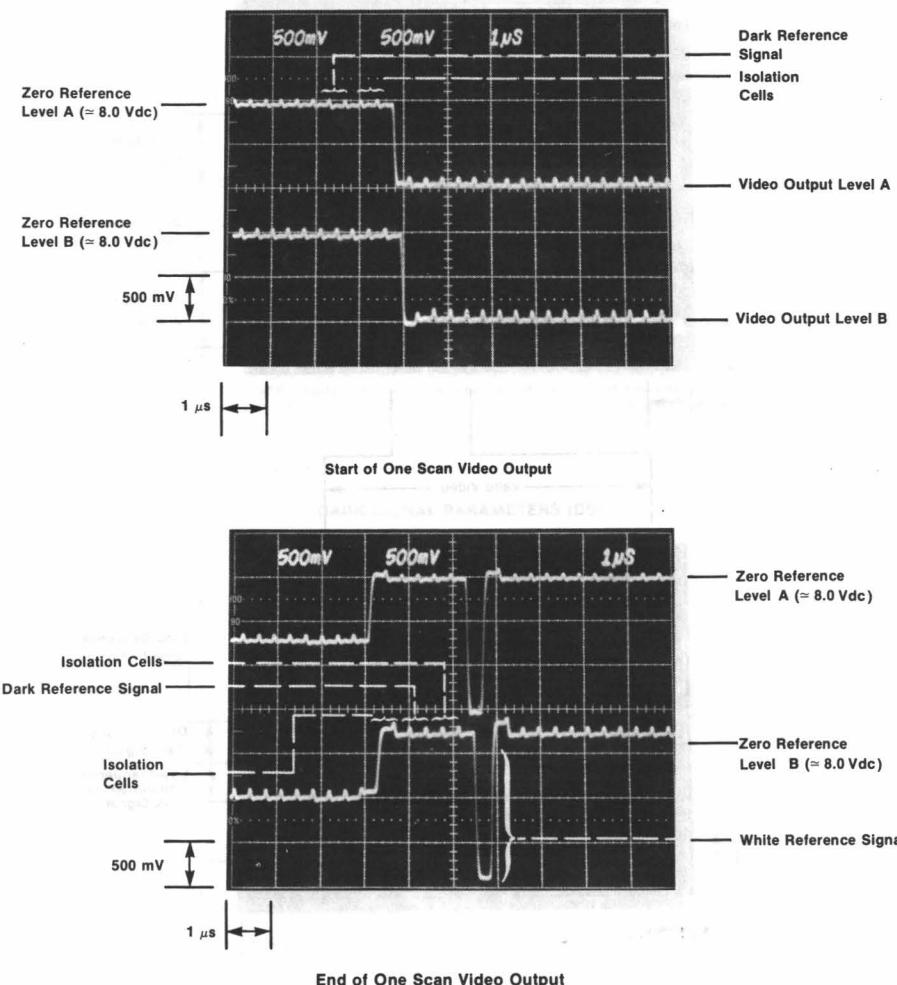

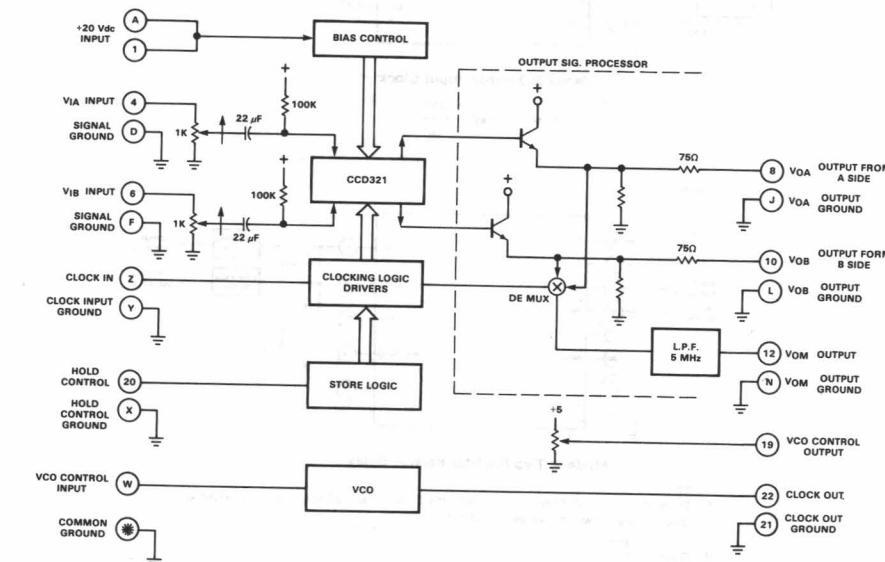

**Transport Clock  $\phi_T$**  — The clock applied to the gates of the CCD transport shift registers to move the charge-packets received from the image sensor elements to the gated charge-detector/amplifier.